# 高誘電率 Ta<sub>2</sub>O<sub>5</sub> 膜のシリコン半導体メモリ用 容量絶縁膜への適用に関する研究

平成 28 年 4 月 神力 博

# 目次

| 第1章 序詞  | A                                                                                | 1  |

|---------|----------------------------------------------------------------------------------|----|

| 1.1 研究  | の背景                                                                              | 1  |

| 1.1.1 I | DRAM メモリセルと容量絶縁膜の動向                                                              | 1  |

| 1.1.2   | 4 メガビット、256 メガビット DRAM 用容量絶縁膜の必要性と課題                                             | 7  |

| 1.2 半導  | 体メモリ用高誘電率絶縁膜の選択                                                                  | 8  |

| 1.2.1   | <b>ド導体メモリ容量絶縁膜用高誘電率誘電体膜の物性</b>                                                   | 8  |

|         | 高誘電率容量絶縁膜の選択                                                                     |    |

| 1.3 研究  | 開発着手時の高誘電率絶縁膜の電気的特性と製造方法のまとめ                                                     | 14 |

| 1.3.1   | 高誘電率絶縁膜の電気的特性の比較評価                                                               | 14 |

| 1.3.2   | `a <sub>2</sub> O <sub>5</sub> 膜の形成方法について                                        | 16 |

|         | 究の目的と本論文の構成                                                                      |    |

|         | <b>ト研究の目的</b>                                                                    |    |

|         | <b>ニ論文の構成</b>                                                                    |    |

| 1.5 参考  | 文献                                                                               | 20 |

|         | 公性スパッター法による Ta <sub>2</sub> O <sub>5</sub> 膜の電気的特性、信頼性評価と<br>イポーラメモリ素子用容量絶縁膜への適用 | 23 |

| 2.1 緒言  |                                                                                  | 23 |

| 2.2 高速  | バイポーラメモリ素子用高容量キャパシタ (容量素子 )の必要性                                                  | 23 |

| 2.2.1   | ノフトエラー対策の動向                                                                      | 23 |

| 2.2.2 1 | 6キロビット高速バイポーラメモリ素子用容量絶縁膜への要求仕様                                                   | 25 |

|         | 方法                                                                               |    |

|         | 〜                                                                                |    |

|         | CVD 法による Ta <sub>2</sub> O <sub>5</sub> 膜の形成                                     |    |

|         | Ta <sub>2</sub> O <sub>5</sub> キャパシタの形成方法                                        |    |

|         | <b>a2O</b> 5 キャハシタの形成刀伝<br>方法                                                    |    |

|         | 刀伝                                                                               |    |

|         | a2O5 戻の物垤分析計価<br>a2O5 キャパシタの電気的特性評価                                              |    |

|         | #2 <b>O</b> 5 ~~~~~0                                                             |    |

|         | 早面酸化膜                                                                            |    |

|         | 映的安定性                                                                            |    |

| ·       | ガィークスポット酸化結晶化モデル                                                                 |    |

|         | [気伝導特性                                                                           |    |

| ,       | — / · · · · · · · · · · · · · · · · · ·                                          |    |

| 2.5.5 界面安定性                                                                                   | 42 |

|-----------------------------------------------------------------------------------------------|----|

| 2.5.6 経時的絶縁破壊信頼性評価(TDDB 特性評価)                                                                 | 44 |

| 2.5.7 静電容量                                                                                    | 45 |

| 2.5.8 高周波特性                                                                                   | 46 |

| 2.6 反応性スパッターTa <sub>2</sub> O <sub>5</sub> 膜の高速バイポーラメモリ素子用容量絶縁膜への適用                           |    |

| 2.7 まとめ                                                                                       |    |

| 2.8 参考文献                                                                                      |    |

| 第 3 章 多結晶シリコン上 Ta <sub>2</sub> O <sub>5</sub> 膜を有するキャパシタの基礎特性                                 | 51 |

| 3.1 緒言                                                                                        |    |

| 3.2 多結晶シリコン上 Ta <sub>2</sub> O <sub>5</sub> キャパシタの検討                                          |    |

| 3.2.1 多結晶シリコン上 Ta <sub>2</sub> O <sub>5</sub> キャパシタの形成方法                                      | 52 |

| 3.2.2 Ta <sub>2</sub> O <sub>5</sub> 膜と多結晶シリコン界面の SiO <sub>2</sub> 膜の成長                       | 53 |

| 3.2.3 多結晶シリコン上 Ta <sub>2</sub> O <sub>5</sub> /SiO <sub>2</sub> キャパシタの TDDB 特性                | 55 |

| 3.2.4 多結晶シリコン上 Ta <sub>2</sub> O <sub>5</sub> /SiO <sub>2</sub> キャパシタの電流-電圧特性                 | 57 |

| 3.3 多結晶シリコン上 Ta <sub>2</sub> O <sub>5</sub> /Si <sub>3</sub> N <sub>4</sub> キャパシタの検討          | 58 |

| 3.3.1 多結晶シリコン上 Ta <sub>2</sub> O <sub>5</sub> /Si <sub>3</sub> N <sub>4</sub> キャパシタの形成方法      | 59 |

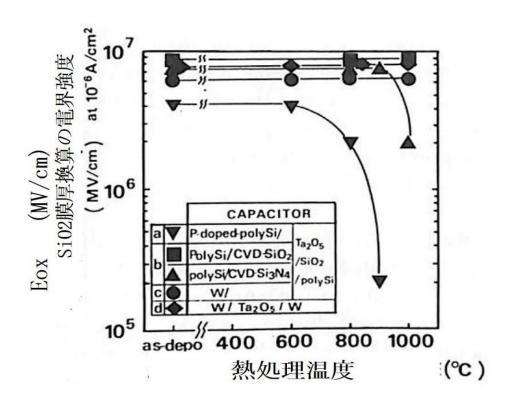

| 3.3.2 多結晶シリコン上 Ta <sub>2</sub> O <sub>5</sub> / Si <sub>3</sub> N <sub>4</sub> キャパシタの熱処理温度依存性 | 60 |

| 3.3.3 多結晶シリコン上 Ta <sub>2</sub> O <sub>5</sub> / Si <sub>3</sub> N <sub>4</sub> キャパシタの電流-電圧特性  | 61 |

| 3.3.4 多結晶シリコン上 Ta <sub>2</sub> O <sub>5</sub> / Si <sub>3</sub> N <sub>4</sub> キャパシタの TDDB 特性 | 61 |

| 3.4 まとめ                                                                                       |    |

| 3.5 参考文献                                                                                      | 64 |

| 第 4 章 積層容量型 DRAM メモリセル用容量絶縁膜への Ta <sub>2</sub> O <sub>5</sub> 膜の適用                            | 66 |

| 4.1 緒言                                                                                        |    |

| 4.2 既存 DRAM プロセスへの適合性評価方法                                                                     |    |

| 4.3 評価方法                                                                                      | 67 |

| 4.3.1 評価用キャパシタ形成方法                                                                            | 67 |

| 4.3.2 熱的安定性、信頼性、膜厚評価方法                                                                        | 69 |

| 4.4 低消費電力高集積 DRAM に適用可能な Ta <sub>2</sub> O <sub>5</sub> 膜を有するキャパシタの                           |    |

| 最大蓄積容量のキャパシタ構造依存性の検討                                                                          | 69 |

| 4.5 Ta <sub>2</sub> O <sub>5</sub> 膜を有するキャパシタの高温プロセス互換性の検討                                    |    |

| 4.6 Ta <sub>2</sub> O <sub>5</sub> 膜を有するキャパシタの TDDB 特性評価                                      |    |

| 4.7 SIS 構造キャパシタの積層容量型 DRAM メモリセルへの適用検討                                                        |    |

| 4.8 光誘起ライフタイム測定による Ta 汚染評価                                                                    | 80 |

| 49 まとめ                                                                                        | 81 |

| 4.10 参考文献                                                                                 | 82  |

|-------------------------------------------------------------------------------------------|-----|

|                                                                                           |     |

| 第5章 二段階熱処理による CVD-Ta₂O₅ 膜の開発と 64 メガビット DRAM への適用                                          | 84  |

| 5.1 緒言                                                                                    | 84  |

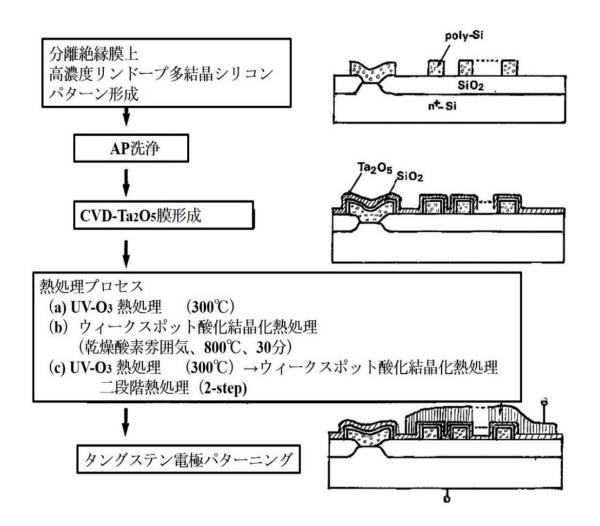

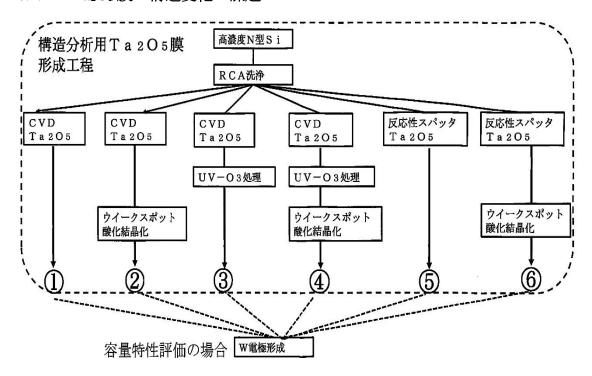

| 5.2 CVD-Ta <sub>2</sub> O <sub>5</sub> 容量絶縁膜形成方法                                          | 86  |

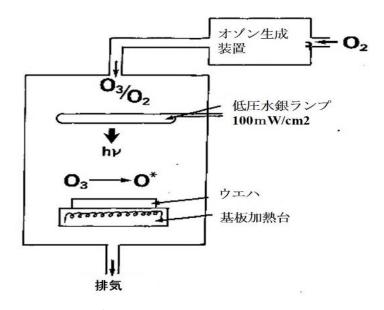

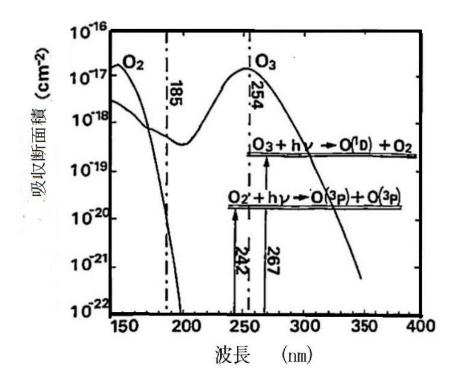

| 5.2.1 UV-O <sub>3</sub> 処理装置                                                              | 86  |

| 5.2.2 Ta <sub>2</sub> O <sub>5</sub> キャパシタの製造工程                                           | 87  |

| 5.2.3 Ta <sub>2</sub> O <sub>5</sub> 膜の評価方法                                               | 88  |

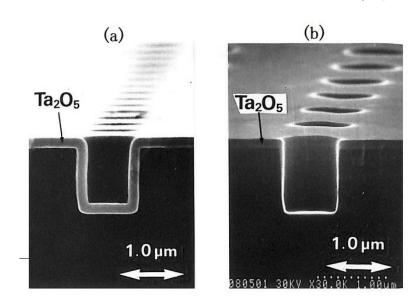

| 5.3 CVD 法による Ta <sub>2</sub> O <sub>5</sub> 膜の被覆性                                         | 89  |

| 5.4 CVD-Ta <sub>2</sub> O <sub>5</sub> 膜の乾燥酸素熱処理の効果                                       | 90  |

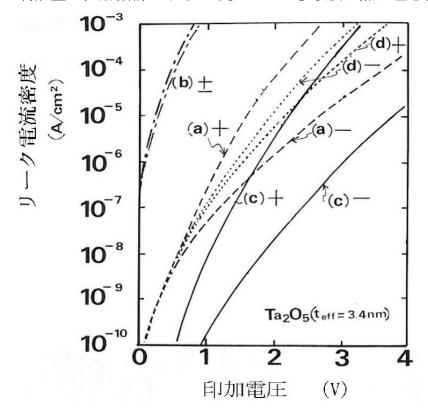

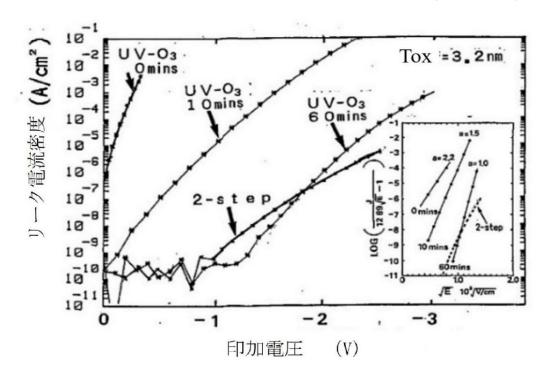

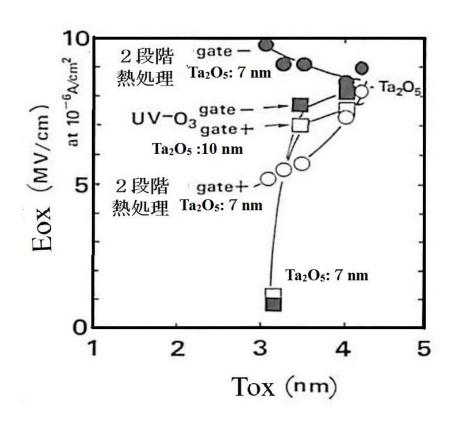

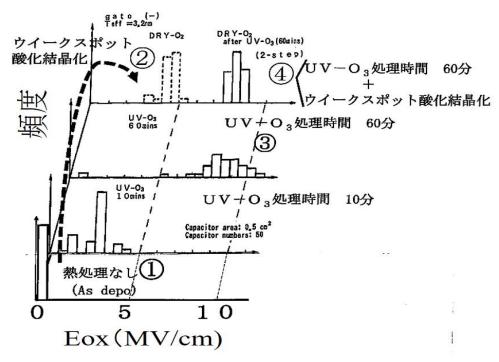

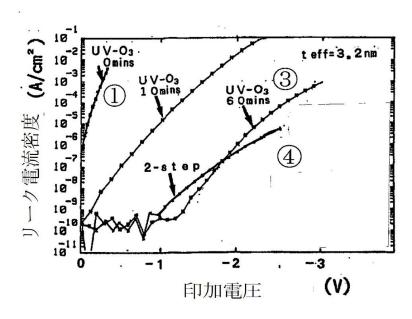

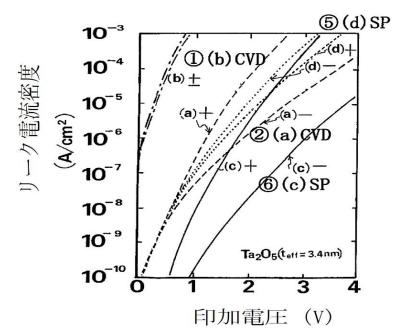

| 5.5 CVD-Ta <sub>2</sub> O <sub>5</sub> 膜のリーク電流低減のための改質処理方法の検討                             | 93  |

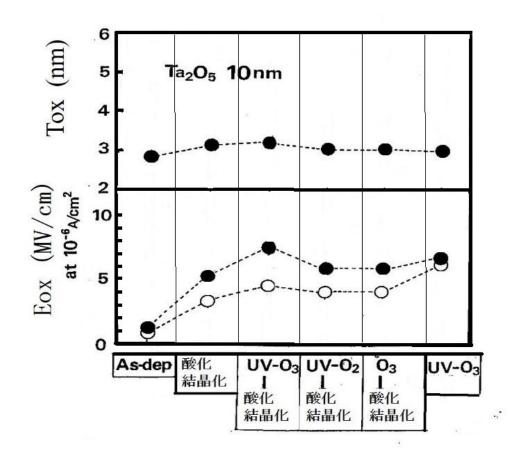

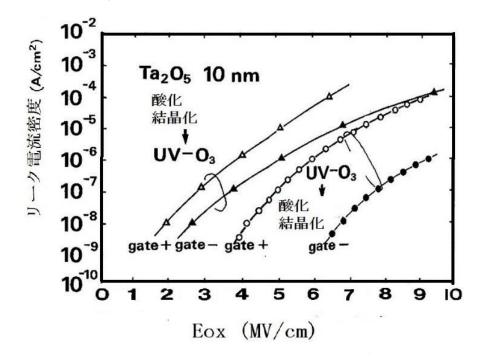

| 5.5.1 二段階熱処理方法の検討(2-step annealing)                                                       | 93  |

| 5.5.2 UV-O <sub>3</sub> , UV-O <sub>2</sub> , O <sub>3</sub> 処理の比較評価                      | 94  |

| 5.5.3 ウィークスポット酸化結晶化熱処理後の UV-O <sub>3</sub> 処理の効果の検討                                       | 93  |

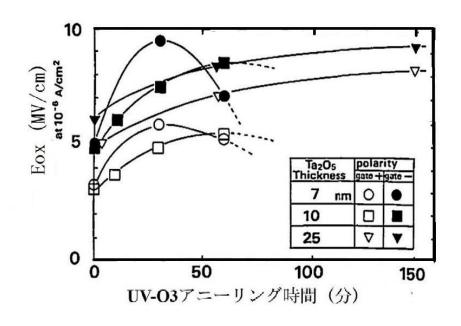

| 5.5.4 CVD-Ta <sub>2</sub> O <sub>5</sub> 膜の Eox の膜厚、UV-O <sub>3</sub> 処理時間依存性             | 97  |

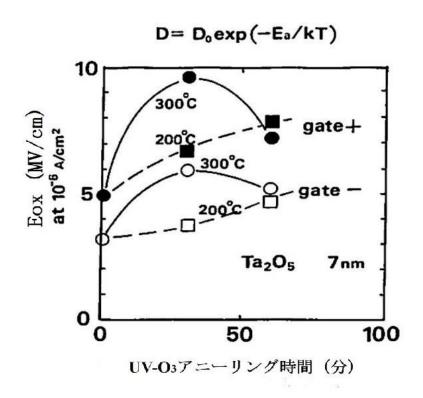

| 5.5.5 CVD-Ta <sub>2</sub> O <sub>5</sub> 膜の Eox の UV-O <sub>3</sub> 処理温度依存性               | 97  |

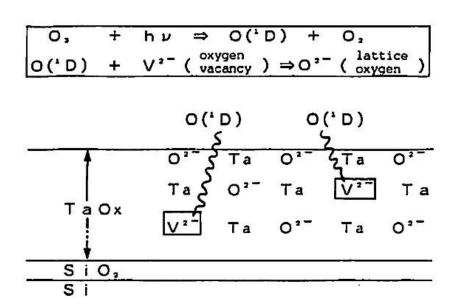

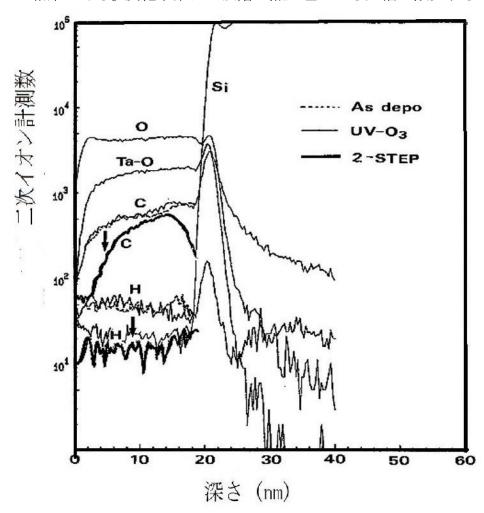

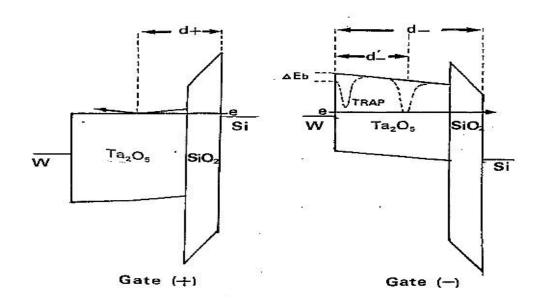

| 5.6 UV-O <sub>3</sub> 処理による CVD-Ta <sub>2</sub> O <sub>5</sub> 膜のリ-ク電流低減モデル               | 98  |

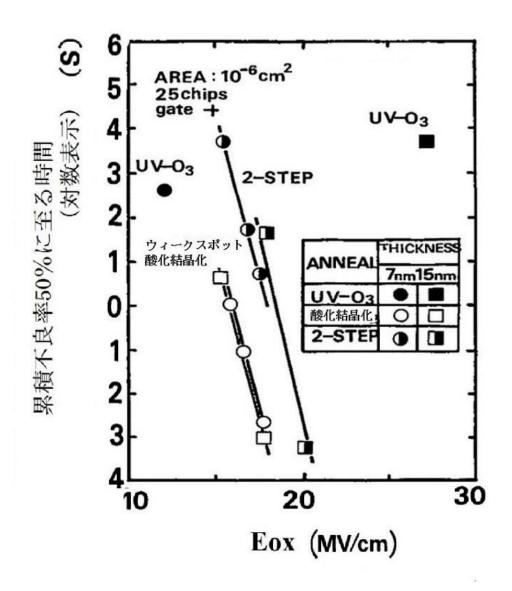

| 5.7 二段階熱処理による CVD-Ta <sub>2</sub> O <sub>5</sub> 膜の欠陥密度低減                                 | 102 |

| 5.8 CVD-Ta <sub>2</sub> O <sub>5</sub> 膜による Eox と SiO <sub>2</sub> 換算膜厚 Tox の適用範囲         |     |

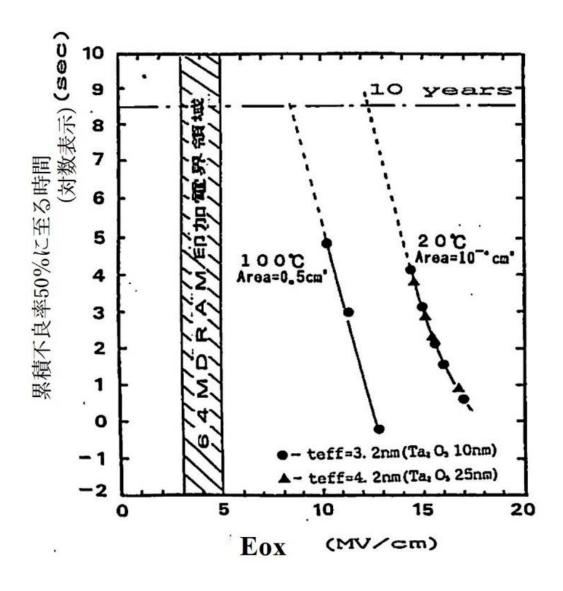

| 5.9 CVD-Ta <sub>2</sub> O <sub>5</sub> 膜の TDDB 特性評価                                       | 106 |

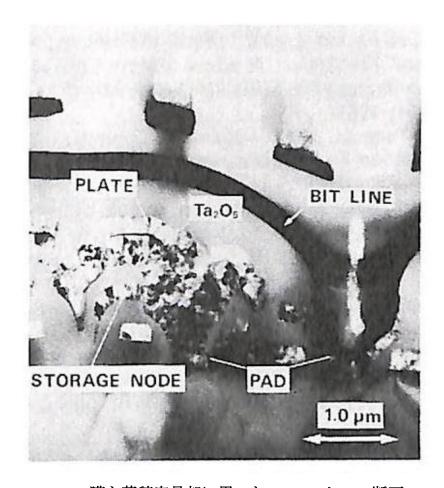

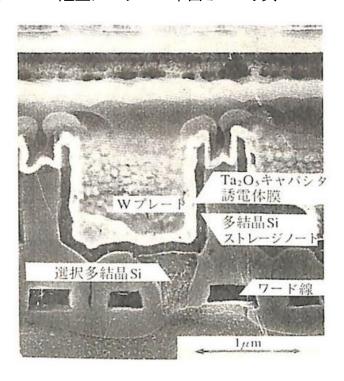

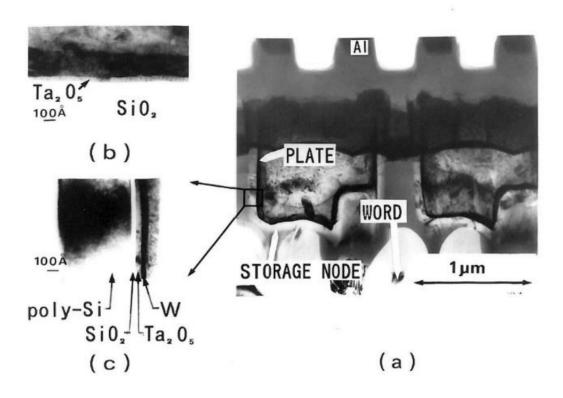

| 5.10 CVD-Ta <sub>2</sub> O <sub>5</sub> 膜を適用した 64 メガビット DRAM の試作                          | 109 |

| 5.10.1 64 メガビット DRAM 用王冠型メモリセルに適用可能な容量絶縁膜の検討                                              | 109 |

| 5.10.2 64 メガビット DRAM 用王冠型メモリセルへの CVD-Ta <sub>2</sub> O <sub>5</sub> 膜の適用                  | 111 |

| 5.11 まとめ                                                                                  | 113 |

| 5.12 参考文献                                                                                 | 114 |

|                                                                                           |     |

| 第6章 極薄 Ta <sub>2</sub> O <sub>5</sub> 膜のウィークスポット酸化結晶化熱処理、活性酸素処理による                        |     |

| 構造、組成変化                                                                                   | 116 |

| 6.1 緒言                                                                                    | 116 |

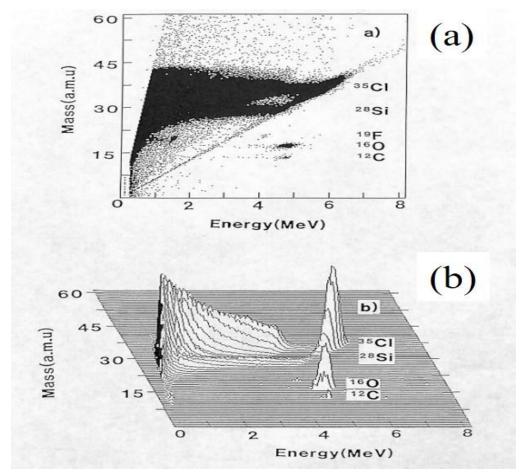

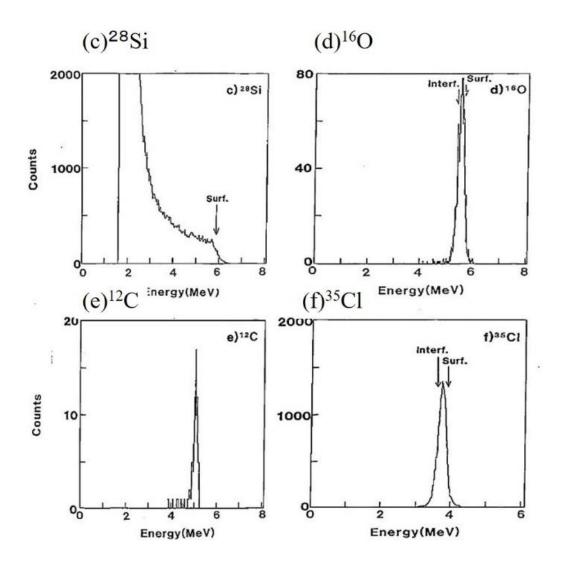

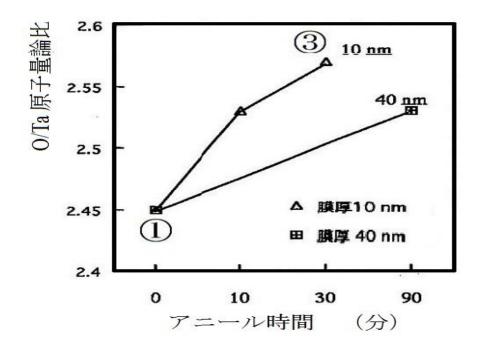

| 6.2 極薄 Ta <sub>2</sub> O <sub>5</sub> 膜野構造解析の課題と極薄膜解析技術の選択                                | 117 |

| 6.2.1 Ta <sub>2</sub> O <sub>5</sub> 膜の構造変化の課題                                            | 117 |

| 6.2.2 極薄 Ta <sub>2</sub> O <sub>5</sub> 構造解析技術の選択                                         | 121 |

| 6.3 熱処理によるスパッターTa <sub>2</sub> O <sub>5</sub> 膜、CVD-Ta <sub>2</sub> O <sub>5</sub> 膜の構造変化 | 127 |

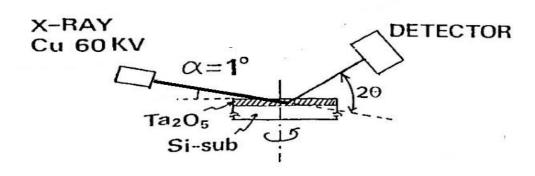

| 6.3.1 微小角入射 X 線回折による極薄 Ta <sub>2</sub> O <sub>5</sub> 膜の評価                                |     |

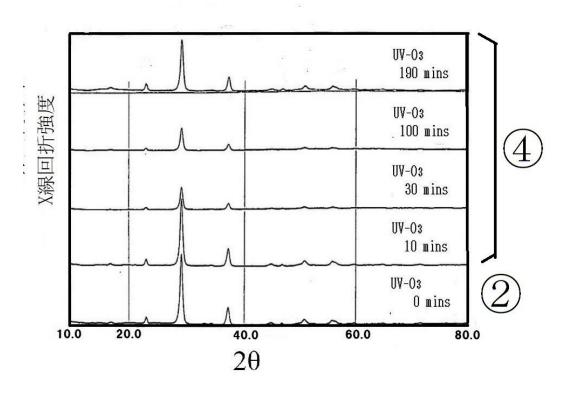

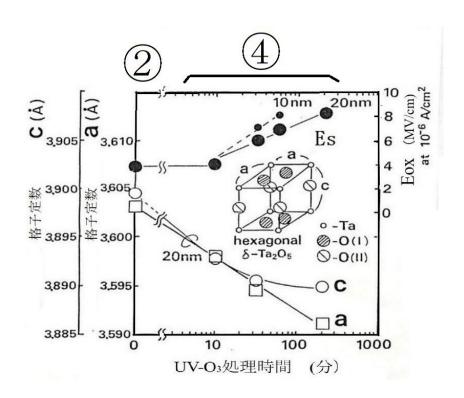

| 6.3.2 CVD-Ta <sub>2</sub> O <sub>5</sub> 膜の結晶構造の UV-O <sub>3</sub> 処理時間依存性                | 129 |

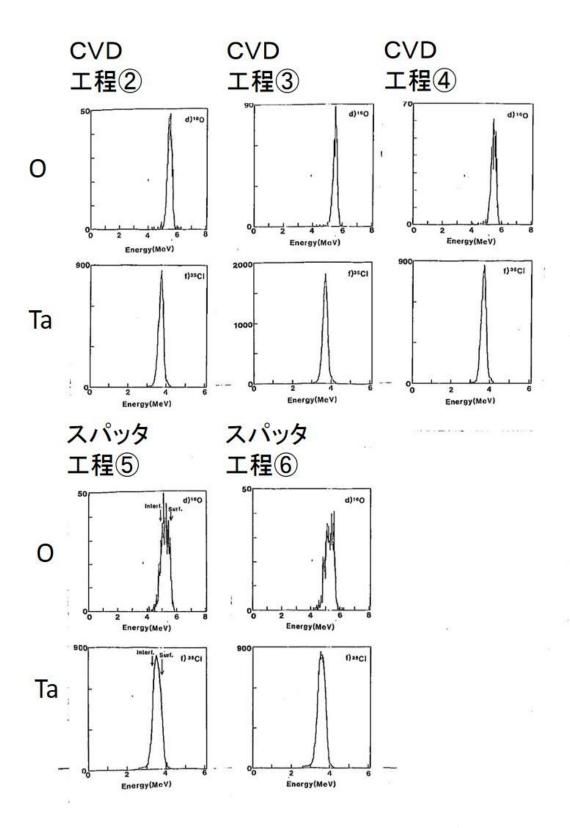

| 6.4 ウィークスポット酸化結晶化熱処理、UV-O3処理による Ta2O5 膜組成比、                                               |     |

| 深さ方向プロファイルの変化                                                                               | 130 |

|---------------------------------------------------------------------------------------------|-----|

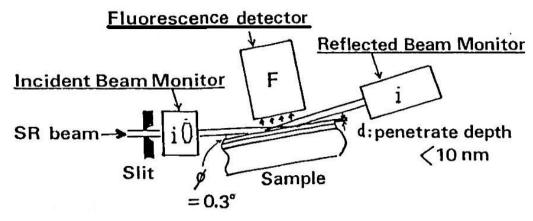

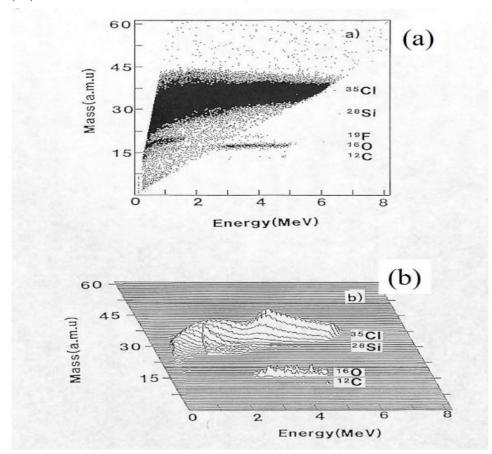

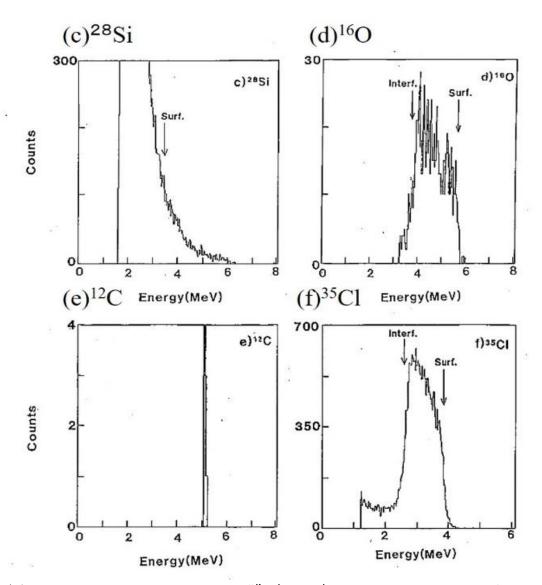

| 6.4.1 ERDA/RBS による O / Ta 組成比の深さ方向プロファイルの評価                                                 | 130 |

| 6.4.2 XPS による O / Ta 組成比の評価                                                                 | 137 |

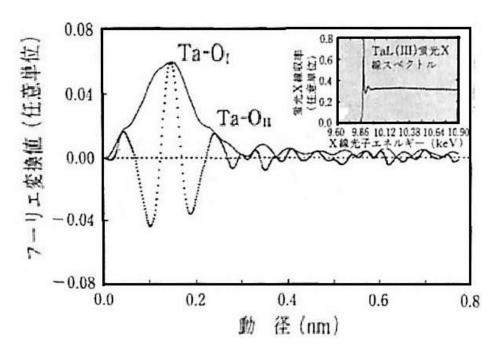

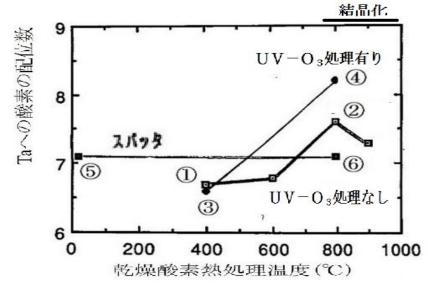

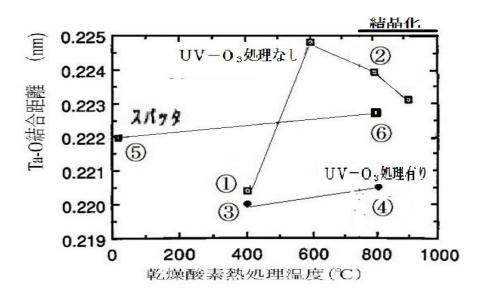

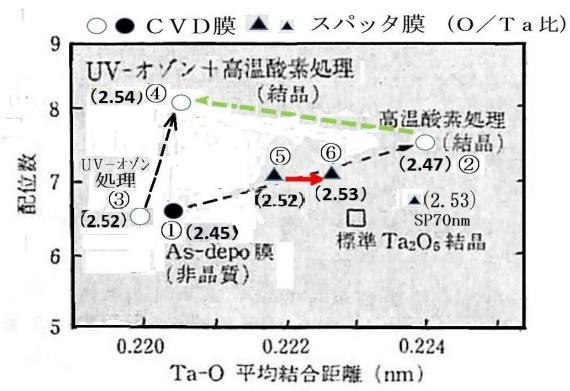

| 6.5 EXAFS による Ta <sub>2</sub> O <sub>5</sub> 膜の Ta への酸素配位数、Ta-O 結合距離の評価                     | 138 |

| 6.6 スパッターTa <sub>2</sub> O <sub>5</sub> 膜、CVD-Ta <sub>2</sub> O <sub>5</sub> 膜の構造変化についての考察  | 140 |

| 6.7 スパッターTa <sub>2</sub> O <sub>5</sub> 膜、CVD-Ta <sub>2</sub> O <sub>5</sub> 膜の結晶構造と酸素欠陥の検討 | 142 |

| 6.8 スパッターTa <sub>2</sub> O <sub>5</sub> 膜、CVD-Ta <sub>2</sub> O <sub>5</sub> 膜の構造変化モデルの検討   | 144 |

| 6.8.1 極薄スパッターTa <sub>2</sub> O <sub>5</sub> 膜の製造工程での構造変化モデル                                 | 144 |

| 6.8.2 極薄 CVD-Ta <sub>2</sub> O <sub>5</sub> 膜の製造工程での構造変化モデル                                 | 144 |

| 6.9 まとめ                                                                                     | 145 |

| 6.10 参考文献                                                                                   | 146 |

| 第 7 章 結論                                                                                    | 147 |

| 謝辞                                                                                          | 149 |

|                                                                                             |     |

# 第1章 序論

# 1.1 研究の背景

# 1.1.1 DRAM メモリセルと容量絶縁膜の動向

シリコン半導体集積回路は R.H.Dennard により提唱されたスケーリング則 (比例縮小則)[1]に従って、微細化がすすめられてきた。シリコン半導体素子 の寸法を比例縮小することによって、素子の高速化、高集積化、低消費電力化が 飛躍的に向上していくことが半導体産業の発展の源泉といえる。本論文で研究 対象とするバイポーラメモリ素子、ダイナミックランダムアクセスメモリ素子 (DRAM: Dynamic Random Access Memories) などのシリコン半導体メモリ素子 においても、メモリ素子の集積度は3年毎に4倍になるのに対し、メモリ素子 面積は3分の1に微細化されてきた。一方、メモリ素子ではスケーリング則に より比例縮小できない要素がある。その代表的なものとしてメモリ素子の蓄積 電荷量が挙げられる。メモリ素子では、半導体素子のパッケージ、配線材料中に 含まれる微量な放射性元素から放出される α 線が半導体基板中で電離を引き起 こし、生成される電荷の流入により、メモリ素子に記憶された情報が意図せずに 書き換えられる現象 (ソフトエラー) を防止しなければならない。従って、メモ リ素子の蓄積電荷量は、この電離によって流入する電荷量に影響されないよう に、十分に大きい蓄積電荷量とする必要があり、素子の微細化とともに蓄積電荷 量を縮小することはできない。最も高集積化が進んでいる DRAM の最大の課題 は、世代毎のメモリセルセル面積の縮小にもかかわらず、微細化されたメモリセ ル内にソフトエラーの防止に必要とされる所定量以上の蓄積電荷量を確保する ことにある。

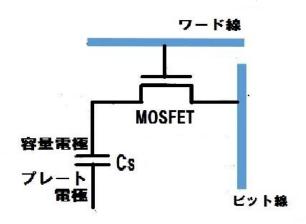

図 1-1 は DRAM メモリセルの基本回路を示している。

図 1-1 DRAM メモリセルの基本的構成

メモリセルはスイッチとなるトランジスタ (MOSFET) と蓄積容量 Cs とから 構成され、蓄積電荷を保持するか、保持しないかにより1ビットの情報を記憶す ることができる。容量部はプレート電極と容量電極の上下の電極に挟まれた容 量絶縁膜により構成される。容量部の蓄積電荷量は容量絶縁膜厚に反比例し、容 量電極表面積に比例する。ソフトエラー防止のために、メモリセルの微細化にも かかわらず、この蓄積電荷量は所定の蓄積電荷量以上とする必要がある。微細化 による蓄積電荷量の減少を容量絶縁膜の薄膜化により補うという方法では、高 電界が印加されることになり、長期信頼性を確保するのは難しくなる[2]、[3]。 4 メガビット DRAM 以降では、低消費電力化の必要性から、スケーリング則に 従って、容量絶縁膜に印加される電界強度が一定となるように、印加電圧の低減 に比例して容量絶縁膜の薄膜化を行なってきた。しかしながら、4 メガビット、 16 メガビット DRAM 素子の容量絶縁膜として使用されてきた Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> 積層膜 は、スケーリング則に従う薄膜化によっても薄膜化の限界に達し、リーク電流 (漏れ電流)が指数関数的に増大するために、容量絶縁膜として適用が困難となる。 64 メガビット DRAM 素子に必要な膜厚では、この薄膜化の限界に達することか ら、Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> 積層膜を高誘電率膜に置き換えることで、長期信頼性を確保しつ つ、リーク電流(漏れ電流)の増加を抑制しながら、スケーリング則に従う実効的 な容量絶縁膜の薄膜化を達成することが期待されてきた。しかしながら、スケー リング則に従って、容量絶縁膜が薄膜化できたとしても、メモリセル面積の微細 化により蓄積電荷量は減少してしまう。ソフトエラー防止に必要な蓄積電荷量 を確保するためには、容量部を立体構造とすることで、メモリセル面積の縮小に もかかわらず、所定の容量電極表面積を確保することが必要となる

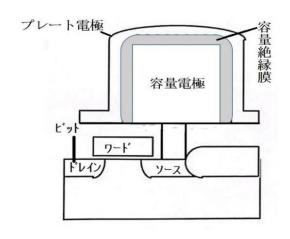

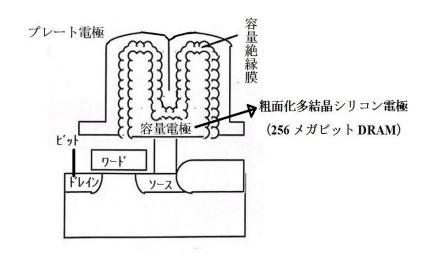

図 1-2 に示す積層容量型メモリセル (Stacked Capacitor Cell: STC CELL) で

図 1-2 積層容量型メモリセル断面模式図

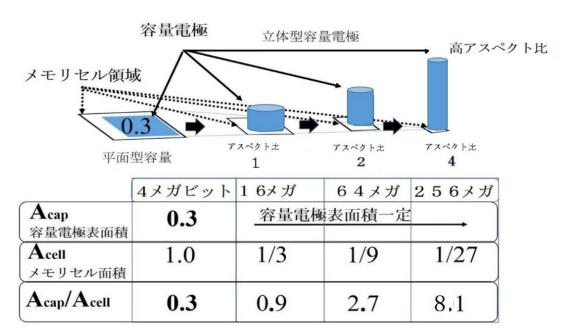

図 1-3 セル面積縮小に伴う立体型容量のアスペクト比の増大についての模式図

は、トランジスタ上に容量部を積層することで容量電極の表面積を増大させ、容 量絶縁膜の薄膜化限界を回避することが提案された〔4〕。図 1-3 はセル面積 Acell を 1/3 に縮小しながら、容量部を立体化して容量電極表面積 Acan を一定に保持す ると仮定した場合に、どの程度の容量部の立体化が必要かを模式的に示してい る。容量絶縁膜厚が薄膜化限界に達したと想定し、容量絶縁膜の膜厚を一定と仮 定した。容量電極は図1-2に示す様な柱状構造であり、容量電極の高さを高くす ることで、容量電極の表面積を増加させている。4 メガビット DRAM の容量部 を平面型と仮定すると、16 メガビットでは、セル面積を 1/3 に縮小するととも に、容量部を立体化することで容量を確保する。この仮定では、64 メガビット DRAM ではメモリセル面積の 2.7 倍の容量電極表面積が必要となる。円柱電極 の直径と高さの比であるアスペクト比は 2 以上となる。しかしながら、製造コ ストを安価にするにはアスペクト比を低くする必要がある。スケーリング則に 従って薄膜化された容量絶縁膜を適用するとしても、印加電圧も比例して低減 されるために、蓄積電荷量が増加することはない。従って、アスペクト比の低い 立体構造容量部でありながら、電極表面積が増加できる工夫が必要となる (図 1-5に示す王冠型メモリセル参照)。

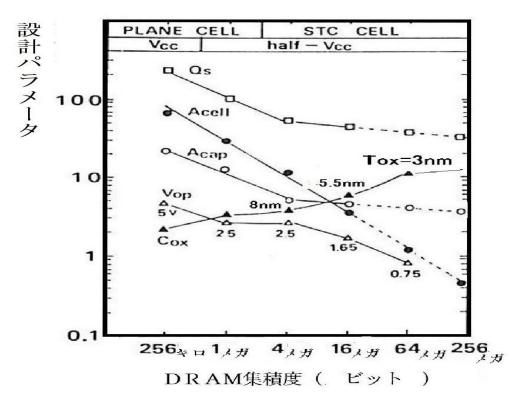

図 1-4 には DRAM 集積度が 256 キロビットから 256 メガビットに至る間の 蓄積電荷量  $Q_s$ 、メモリセル面積  $A_{cell}$ 、容量電極表面積  $A_{cap}$ 、動作電圧  $V_{op}$  などの設計パラメータの変遷を示している。蓄積電荷量  $Q_s(fC)$ は、近似的には(1 - 1)式に示すように、容量電極表面積:  $A_{cap}$  と動作電圧:  $V_{op}$  に比例し、容量絶縁膜の膜厚: T に反比例する、

$$Q_{s} = \varepsilon_{O} \cdot \varepsilon_{T} \cdot \frac{A_{cap}}{T} \cdot V_{OP} = \alpha \cdot \varepsilon_{O} \cdot \varepsilon_{T} \cdot \frac{A_{cell}}{T} \cdot V_{OP}$$

(1 - 1)

ここで、 $\epsilon_0$ : 真空中の誘電率、 $\epsilon_r$ : 比誘電率であり、 $\alpha$ : 立体化係数である。

$$\alpha = \frac{A_{cap}}{A_{cell}} \tag{1-2}$$

| メモリセル面積 Acell, | 電極表面積Acap | $(\mu m^2)$ |

|----------------|-----------|-------------|

| 苦積電荷量          | Qs        | (fC)        |

| 動作電圧           | Vop       | (V)         |

| 面積当たりの容量       | Cox       | fF/µm²      |

図 1-4 DRAM 集積度 vs 蓄積電荷量  $Q_s$ 、メモリセル面積  $A_{cell}$ 、実効キャパシタ面積  $A_{cap}$ 、動作電圧  $V_{op}$  関係、面積あたりの容量 Cox(1/Tox に比例)

膜もスケーリング則により、容量絶縁膜の電界強度が一定となるように薄膜化するのが望ましい。(1-1)式から、スケーリング則による 4 メガビット以降の動作電圧 Vop の低下、これに比例する容量絶縁膜 T の薄膜化は、Vop/T を一定にすることに相当するので、 $Q_s$  の増減に影響しない。従って、メモリセル面積  $A_{cell}$  の微細化にもかかわらず、 $Q_s$  を一定とするためには、容量電極表面積  $A_{cap}$  を所定量に保つ必要がある。つまり、世代毎に  $\alpha$  を少なくとも  $\alpha$  倍とする必要がある。

従って、所定の蓄積電荷量を得るためには、下記の(a)、(b)の方法により蓄積電荷量を確保することになる[7]。

- (a) 立体化係数 α を少なくとも世代毎に 3 倍に増加(Acap/Acell を増加)

- (b) 容量絶縁膜の薄膜化(少なくともスケーリング則から予測される膜厚)

容量絶縁膜の膜厚をスケーリング則に従って薄膜化できない場合には、立体 化係数  $\alpha$  を 3 倍以上に大きくする必要があり、製造の難易度、コストが増加し てしまう。それぞれの技術の推移について次に述べる。

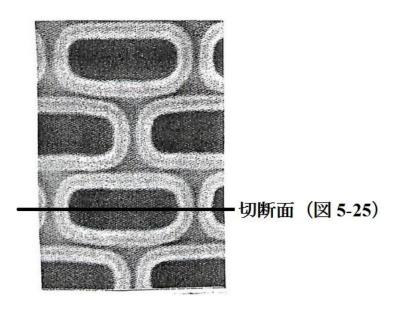

# (a) 立体化係数 α の増加

図 1-4 に記載のように、1 メガビット DRAM までは平面容量型メモリセル (PLANE CELL)で十分な容量を確保できたが、4 メガビット、16 メガビット DRAM では、積層容量型メモリセル( STC CELL )を導入することで立体化係 数を3倍に増加させ、Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>積層膜が薄膜化限界に達することを回避するこ とに成功した。64メガビット DRAM 以降では、ソフトエラー防止を考慮して、 蓄積電荷量が少なくとも 30 fC.以上となるように、容量部の立体化係数 α を増加 させることで、必要な容量電極表面を確保する必要があった。16 メガビット DRAM までは、円柱型容量電極を有する積層容量型メモリセル構造を適用した が、64 メガビット DRAM では、アスペクト比の増大を抑制するために、図 1-5 に示す王冠型電極 ( CROWN ) を有する積層容量を検討した〔6〕。王冠型の容 量電極は容量電極の外表面に加え、内表面も容量電極表面として用いることで、 容量電極表面の大きさを円柱構造よりも約2倍に増加することができる[8]。 この王冠型電極を有する容量部の  $\alpha$  (= $A_{cap}/A_{cell}$ ) は 2.7 となった〔7〕。図 1-3 に 記載の 64 メガビット DRAM 用メモリセル用の円柱型電極を有する容量構造に よるモデル化によればαは2.7となり、王冠型電極を有する容量構造により、ア スペクト比を低くしながら、必要な蓄積電荷量を確保できる。更に、256メガビ ット DRAM では、図 1-5 の模式図に示す様に、容量電極である多結晶シリコン 表面を粗面化した粗面化多結晶シリコン (図 5-6 参照)により表面積を 2 倍に

図 1-5 王冠型 ( CROWN) 容量部断面模式図

増加させ [9]、アスペクト比を増加することなく、 $\alpha$  を 7.5 に増加できる。図 1-3 に記載の 256 メガビット DRAM 用メモリセル用の円柱型電極を有する容量構造のモデル化では  $\alpha$  は 8.1 であり、王冠型電極と粗面化多結晶シリコン電極の組み合わせにより、アスペクト比を低く保ちながら、256 メガビット DRAM に必要な蓄積電荷量を確保できる。

本論文に述べる高誘電率容量絶縁膜、王冠型容量電極、粗面化多結晶シリコン電極を組み合わせることで、64 メガビット、256 メガビット DRAM の製品化を可能とすることができた。この高誘電率容量絶縁膜と王冠型容量電極の組み合わせが、現在の DRAM の基本構成となっている。

#### (b) 容量絶縁膜の薄膜化

容量絶縁膜の薄膜化の推移を述べるにあたり、比誘電率の異なる各種の材料からなる容量絶縁膜を比較するために、 $SiO_2$ 換算膜厚  $T_{OX}$  と  $SiO_2$  換算膜厚での電界強度  $E_{OX}$  を定義する。本論文ではこのパラメータにより、各種の容量絶縁膜の特性を容易に比較できる。

通常、容量部を試作する場合には、容量値 C が測定される。容量値は下式で 記載される。

$$C = \varepsilon_0 \cdot \varepsilon_r \cdot \frac{A}{T} (F) \tag{1 - 3}$$

ここで、 $\epsilon_0$ : 真空中の誘電率、 $\epsilon_r$ : 比誘電率、A:電極表面積、T: 容量絶縁膜厚とする。従って、容量絶縁膜の比誘電率が定まっていれば、容易に T が得られるが、実際の容量では比誘電率はプロセス条件で変化する。そこで、比誘電率  $\epsilon_r$  を  $SiO_2$  膜の比誘電率  $\epsilon_s$  = 3.82 とすることにより、容量絶縁膜の  $SiO_2$  換算膜

厚Toxを求めることができる。

$$C = \varepsilon_{O} \cdot \varepsilon_{r} \cdot \frac{A}{T} (F) = \varepsilon_{O} \cdot \varepsilon_{S} \cdot \frac{A}{T_{OX}}$$

(1 - 4)

一方、容量絶縁膜の絶縁性を評価する場合に、所定の電流が流れる印加電圧を V として、膜厚に依存しない電界強度に換算して比較するのが便利である。電界強度は下式により求められる。

$$E = \frac{V}{T} \tag{1-5}$$

しかしながら、比誘電率だけでなく、膜厚自体もプロセスにより変動するので、 $SiO_2$  換算膜厚 Tox と所定の漏れ電流となる印加電圧 V より、 $SiO_2$  換算膜厚での電界強度 Eox を算出して、容量絶縁膜の性能を比較するのが望ましい。

$$E_{OX} = \frac{V}{T_{OX}} \tag{1-6}$$

本論文では、 $SiO_2$  換算膜厚 Tox、 $SiO_2$  換算膜厚での電界強度 Eox 用いて、容量絶縁膜の性能の良否について議論を進める。

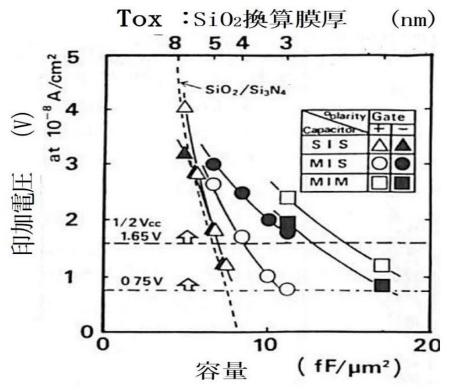

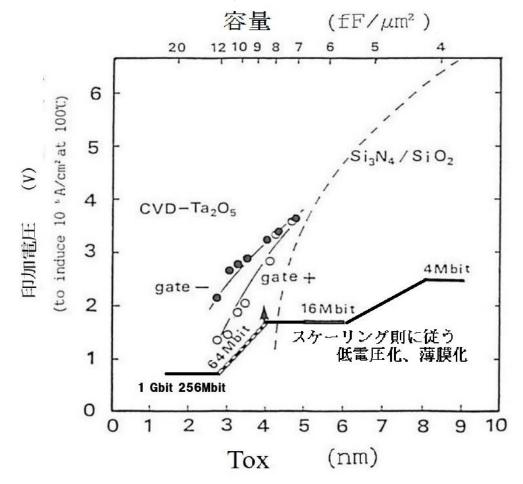

容量絶縁膜の薄膜化の推移を図 1-4 に示している。スケーリング則に従って、電源電圧を低下するとともに、容量絶縁膜に印加される電界強度 Eox がほぼ一定となるように容量絶縁膜を薄膜化することになる。容量絶縁膜に印加される電圧は 1/2Vcc 方式により、4 メガビット、16 メガビット、64 メガビット DRAM へ高集積化されるにつれ、電源電圧の半分の 2.5 V、1.65 V、0.75 V に低電圧化されている。従って、4 メガビット DRAM では多結晶シリコン電極上の  $Si_3N_4/SiO_2$  積層膜は  $SiO_2$  換算膜厚 Tox は 8 nm であり、16 メガビット DRAM では 5.5 nm まで薄膜化された。 $Si_3N_4/SiO_2$  積層膜を 5 nm 以下に薄膜化する場合には、漏れ電流が指数関数的に増大する。薄膜化により、直接トンネリング電流が雪崩的に増大することにより、容量絶縁膜として適用することはできない [10]。スケーリング則によれば、64 メガビット DRAMでは、電源電圧の低下に応じて、容量絶縁膜の目標とされる  $SiO_2$  換算膜厚 Tox は 3 nm 以下となる。この薄膜化によっても、低い漏れ電流を保ちながら、優れた長期信頼性を有する容量絶縁膜が必要となる。

# 1.1.2 64 メガビット、256 メガビット DRAM 用容量絶縁膜の必要性と課題

本研究の目的は、64 メガビット、256 メガビット DRAM 素子の実現に必要な容量絶縁膜を開発することにある。16 メガビット DRAM まで適用された  $Si_3N_4/SiO_2$  積層膜は薄膜化の限界に達し、新たな誘電体材料により、64 メガビット、256 メガビット DRAM に必要な  $SiO_2$  換算膜厚 Tox が 3 nm 以下となる容量 絶縁膜を実現することが必要となった。

キャパシタに蓄積できる電荷量 Q は(1-1)式で表すことができる。従 って、ソフトエラーを防止するのに必要な蓄積電荷量は、動作電圧 Vop、電極面 積に加えて、容量絶縁膜厚Tによって決まる。スケーリング則に従う場合には、 Vop/T はほぼ一定となるので、所定の蓄積電荷量は立体化係数  $\alpha$ (=Acap/Acell) により調整することになる。スケーリング則に従う薄膜化ができない場合には、 より電極表面積を増大させる必要がある。本論文では、Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> 積層膜を高誘 電率容量絶縁膜に置き換えることで、漏れ電流を所定の電流値以下としながら、 スケーリング則に従う薄膜化が可能となることを示す。また、高誘電率容量絶縁 膜を容量絶縁膜として適用するとしても、固体素子の動作の信頼性を確保する には、必要とされる周波数領域における誘電損失が小さく、十分な絶縁破壊信頼 性が得られる必要がある。また、Si 半導体メモリの素子形成プロセスに適用す るには、高温プロセスへの耐熱安定性、材料加工の容易さ、半導体性能を低下さ せることのない程度の純度などを兼ね備えていることが必要である。また、超高 集積、超微細な素子を形成するのが目的であるので、従来の固体素子で用いられ ている誘電体膜と比較して、その膜厚は 10 nm 以下の極薄膜となるため、制御 性の良い薄膜形成技術の選択も極めて重要である。また、高誘電率膜の採用は、 スケーリング則から必要とされる容量絶縁膜の SiO<sub>2</sub> 換算膜厚の薄膜化を可能と するものであるが、ソフトエラーを防止するための蓄積電荷量を確保するため には、立体型容量構造との組み合わせが必要である。従って、高誘電率容量絶縁 膜を採用しても、良好な被覆性を可能とする成膜方法が必要となる。

本研究で目標とすべき容量絶縁膜の特性を以下にまとめる。

- ・SiO<sub>2</sub> 換算膜厚 Tox が 3 nm 以下であって、動作電圧で低い漏れ電流が可能。

- ・高誘電率容量絶縁膜であっても、誘電損失が小さく、安定した誘電体膜。

- ・高信頼性(薄膜領域でも低欠陥密度、優れた絶縁破壊信頼性)。

- ・DRAM プロセスへの適合性(耐熱性、加工性、汚染なし)。

- ・立体型容量構造での良好な被覆性、膜厚制御性を可能とする成膜方法。 上記の特性を満足する容量絶縁膜が必要となる。

# 1.2 半導体メモリ用高誘電率容量絶縁膜の選択

1.1 節に示す様に、 $SiO_2$ ,  $Si_3N_4/SiO_2$  積層膜の薄膜化の限界を超える  $SiO_2$  換算 膜厚 3 nm 以下の薄膜化を可能とする誘電体材料のうち最適な材料の選択を行う必要があった。1.2.1 節では誘電体薄膜の物性について検討し、主に金属酸化物 誘電体のなかで、比誘電率が大きく、かつ、電波領域において安定な誘電特性を示す誘電体材料について検討した。1.2.2 節では、1.2.1 節において選択した材料 から、比誘電率が 20 以上であり、バンドギャップが比較的大きく、誘電損失が小さい酸化タンタル膜を研究の対象として選択した理由を明らかとする。

# 1.2.1 半導体メモリ容量絶縁膜用高誘電率誘電体膜の物性

誘電性は誘電分極より生じ、誘電分極は電子分極、イオン分極、配向分極、 界面分極、空間電荷分極などからなっている。電子分極は原子内の原子核と周囲 の電子群とが電界 E により変位し、双極子モーメントが発生することによる。

$$\mu_e = \alpha_e E$$

$\alpha_e = 4 \pi \epsilon_0 R^3$   $(1 - 7)$

œは電子分極率であり、核外電子群の実効半径 R の 3 乗に比例する。従って、 原子番号が増加すると α は増加し、誘電率も増加する。電子分極は電子の変位 であり、その誘電分散周波数は可視光線から紫外線の振動数領域にある。一方、 イオン分極はイオン性結晶とか分子内の共有結合がイオン性を有する場合に発 生する。イオン化した正と負の原子が静電界により反対方向に変位し、正、負イ オン間の距離とか、分子内の原子間距離が変化して双極子モーメントが発生す ることによる。イオン分極では原子の変位によるため、赤外領域に誘電分散周波 数がある。配向分極は共有結合にイオン性がある場合に、各分子内でのこれらの 双極子を合計し、合成双極子がゼロでない場合には、静電界が加わると、熱運動 にさからって、各分子内の合成双極子は電界方向に配向する。配向分極は分子配 向によるので動きにくいために、電波周波数領域に誘電分散を生ずる周波数が ある。界面分極、空間電荷分極についても同様である。電子分極、イオン分極が 通常の電波周波数領域では殆ど変動しないのに対し、配向電極、界面分極、空間 電荷分極は誘電体の内部構造を反映して、分散周波数は電波領域において変動 する。従って、誘電体膜の選択に当たっては、化学結合の性質を反映した電子分 極、イオン分極により高い誘電率となる誘電体に着目すべきである。電子分極や イオン分極を示す物質を振動電界中においた時の誘電的性質は、その物質内に 含まれる電荷が調和振動するのと同等であると考えて説明することができる。

電荷 Q、質量 M の粒子の振動電界

$$E=E_0 \exp(-iwt) \qquad (1 - 8)$$

の中に置かれた時の運動方程式

$$\frac{d^2 x}{d^2 t^2} + \gamma \frac{d x}{d t} + w_0^2 x = \frac{q}{m} E_0 \exp(-iwt) \qquad (1 - 9)$$

ここで、 $w_0$ : 固有振動数、 $\gamma$ ; 荷電粒子を受ける制動力の定数 (1-9) 式を解くと

$$X(t) = \frac{qE_0}{m} \frac{\exp(-iwt)}{(w_0^2 - w^2 - iyw)}$$

(1 - 1 0)

誘導双極子モーメントは qx(t)となる。誘電体が単位体積当たりn個の原子あるいは分子からなるとすれば、その分極は nqx に等しい。誘電体が電界 E の中に置かれた場合の分極 P は

$$P = nqx = nqX(t) \qquad (1 - 1 1)$$

で与えられる。Lorentz の式によれば

$$\varepsilon_0 \, \varepsilon_{\gamma}^* \mathbf{E} = \varepsilon_0 \, \mathbf{E} + \mathbf{P} \tag{1 - 1 2}$$

従って、 $\varepsilon_{\nu}^{*}$ は複素比誘電率

$$\varepsilon_{\gamma}^* = \varepsilon_{\gamma}' - i\varepsilon_{\gamma}'' \tag{1 - 1 3}$$

とおくと

$$\varepsilon'_{\gamma} = 1 + \frac{(nq2)}{\varepsilon_0 \cdot m} \cdot \frac{(w_0^2 - w^2)}{(w_0^2 - w^2)^2 + \gamma^2 \cdot w^2)}$$

(1 - 1 4)

$$\varepsilon''_{\gamma} = \frac{nq^2}{\varepsilon_0} \cdot \frac{\gamma w}{(w_0^2 - w^2)^2 + \gamma^2 \cdot w^2)} \tag{1 - 1 5}$$

$\mathbf{w}=\mathbf{w}_{o}$  の場合には、 $\mathbf{\epsilon'}_{\gamma}-1$ は0となり、 $\mathbf{\epsilon''}_{\gamma}$ は極大となる。エネルギーの吸収は  $\mathbf{\epsilon''}_{\gamma}$ に比例するから、 $\mathbf{w}_{o}$ で電磁波の吸収は極大を示す。非金属固体化合物は電子 励起に加えて、赤外領域の振動モードを持っている。従って、 $\mathbf{\epsilon''}_{\gamma}$ は電子吸収体

付近と赤外活性な振動周波数の付近で変化する。静電界が印加される場合には、w=0により、

$$\varepsilon'_{\gamma} = 1 + \frac{(\text{nq2})}{\varepsilon_0 \cdot m \cdot w_0^2} \qquad \varepsilon''_{\gamma} = 0 \qquad (1 - 1 6)$$

$\varepsilon'_{\gamma}$  が静電比誘電率を与える。Maxwell の理論により、誘電体中の光の速度が真空中の光の速度よりも小さいのは、分極可能な電子が電磁波の振動電場との相互作用することによるからであり、物質の屈折率 N と電子分極による誘電率 $\varepsilon_{opt}$ の関係は下式で示すことができる。

$$\varepsilon_{opt} = \varepsilon'_{\gamma} (w = 0) = N^2 \qquad (1 - 1 7)$$

電子分極のみを考慮すればよい単元素の誘電体の場合には、woは電子励起エネ ルギーの平均値、つまり、平均のエネルギーギャップに相当する量とみなすこと ができる。従って、電子分極による比誘電率が大きい原子番号の大きい誘電体は、 原子番号の増加とともに隣接原子間の相互作用が増大し、結合性、非結合性軌道 のバンド幅が広がり、バンドギャップが減少する。(1-16)式から、バンド ギャップが減少すれば、比誘電率が増加することが一般的であることがわかる。 比誘電率が電子分極によって決定される共有結合性のダイヤモンド、Si、Ge、Sn の系列のバンドギャップは、ダイヤモンド構造が可能とする S 軌道、P 軌道より なる SP3 混成軌道の結合性、非結合性のバンド幅が広がり、バンドギャップは 5.5, 1.1, 0.7, 0.1 eV となる。一方、比誘電率は 5.7, 12.0, 16.0, 24.0 となる。 電子分極による誘電率 $\epsilon_{ont}$ の増加はバンドギャップの減少につながり、絶縁性能 は低下することを示唆している。次に、イオン分極の誘電率への寄与について検 討する。 イオン分極は異なる元素からなる結合において生ずるから、2 元以上の 化合物がここでは対象となる。これらの化合物の誘電率は、電子分極による誘電 率 ε<sub>oot</sub> よりも大きな値を示す。典型的なイオン結晶であるハロゲン化アルカリで はイオン分極は大きく、例えば NaCl では電子分極による比誘電率が 2.3 に対し て、イオン分極を含むと 5.6 となる。イオン分極の大きさの目安をみるために、 ポーリングの電気陰性度を考慮することができる。図 1-6 はポーリングの電気陰 性度表である。A原子とB原子が純粋な共有結合をする場合に対する結合エネ ルギーに対して、イオン結合に相当する結合エネルギーの相対的な大きさは下 式で推測できる。

$$\Delta E(A - B) = K(X_P^A - X_P^B)^2$$

(1 - 1 8)

| 族周期    | 1          | 2          | 3          | 4          | 5         | 6          | 7  | 8          | 9         | 10         | 11                                     | 12        | 13         | 14         | 15         | 16         | 17         | 18         |

|--------|------------|------------|------------|------------|-----------|------------|----|------------|-----------|------------|----------------------------------------|-----------|------------|------------|------------|------------|------------|------------|

| 1      | H<br>2.20  |            |            |            |           |            |    |            |           |            |                                        |           |            |            |            |            |            | He         |

| 2      | Li<br>0.98 | Be<br>1.57 |            |            |           |            |    |            |           |            |                                        |           | B<br>2.04  | C<br>2.55  | N<br>3.04  | O<br>3.44  | F<br>3.98  | Ne         |

| 3      | Na<br>0.93 | -          |            |            |           |            |    |            |           |            |                                        |           | AI<br>1.61 | Si<br>1.90 | P<br>2.19  | S<br>2.58  | CI<br>3.16 | Ar         |

| 4      | K<br>0.82  |            |            | Ti<br>1.54 | V<br>1.63 |            |    | Fe<br>1.83 |           | Ni<br>1.91 |                                        | 20.00     | Ga<br>1.81 |            | As<br>2.18 | Se<br>2.55 | Br<br>2.96 | Kr<br>3.00 |

| 5      | Rb<br>0.82 | Sr<br>0.95 | Y<br>1.22  | Zr<br>1.33 | Nb<br>1.6 | Mo<br>2.16 |    |            |           | Pd<br>2.20 | _                                      |           | In<br>1.78 | Sn<br>1.96 |            | Te<br>2.1  | I<br>2.66  | Xe<br>2.6  |

| 6      | Cs<br>0.79 | Ba<br>0.89 | *          | Hf<br>1.3  | Ta<br>1.5 | W<br>2.36  |    | Os<br>2.2  |           |            |                                        | 200       |            | Pb<br>2.33 | Bi<br>2.02 | Po<br>2.0  | At 2.2     | Rn         |

| 7      | Fr<br>0.7  | Ra<br>0.9  | **         | Rf         | Db        | Sg         | Bh | Hs         | Mt        | Ds         | Rg                                     | Cn        | Uut        | FI         | Uup        | Lv         | Uus        | Uuo        |

| ランタノイド | *          | La<br>1.1  | Ce<br>1.12 | Pr<br>1.13 |           | Pm<br>1.13 |    |            | Gd<br>1.2 | Tb<br>1.1  | ************************************** |           |            | Tm<br>1.25 |            | Lu<br>1.27 |            |            |

| アクチノイド | **         | Ac<br>1.1  | Th<br>1.3  | Pa<br>1.5  | U<br>1.38 |            |    | Am<br>1.13 |           |            | Cf<br>1.3                              | Es<br>1.3 | Fm<br>1.3  | Md<br>1.3  | No<br>1.3  | Lr         |            |            |

図 1-6 ポーリングの電気陰性度 (ポーリング"化学結合論"より)

従って、以上の検討から、原子量が比較的大きいことにより電子分極が大きく、かつ、イオン分極が大きいイオン性結合性を有しており、電波領域において安定した高い誘電率となる材料が容量絶縁膜用の高誘電率材料として選択すべき材料である。

#### 1.2.2 高誘電率容量絶縁膜の選択

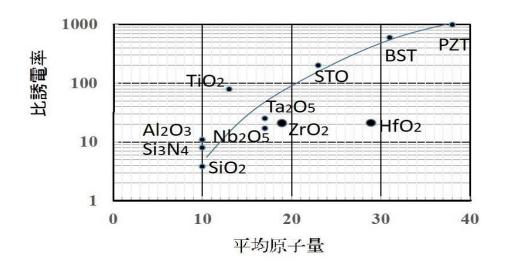

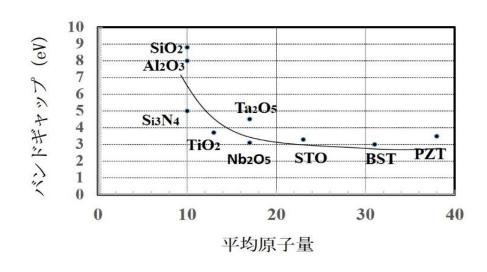

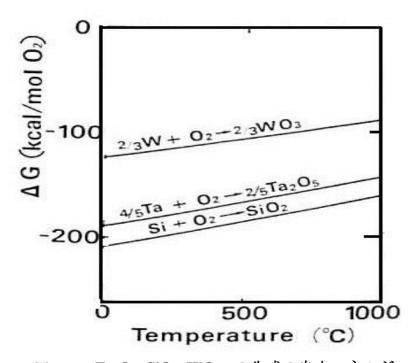

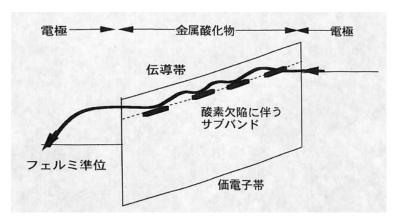

2 元酸化物の場合も単元素の誘電体の場合と同様に、化合物を構成する原子の平均原子番号が大きくなると誘電率は増加し、バンドギャップが小さくなることが報告されている [11]。1.2.1 節で示したように、電子分極が大きいのはよ

り原子番号が大きい元素であるが、更にイオン性化合物であって、イオン分極が大きい酸化物となる Ti、Zr、Nb、Hf、Ta、Y が望ましいことを示した。これらの酸化物、および、高誘電率となる 3 元、4 元化合物について、平均原子量と比誘電率、平均原子量とバンドギャップの関係を図 1-7、図 1-8 にそれぞれ示した。 ZrO<sub>2</sub>、HfO<sub>2</sub>については P.J.Harrop 等のデータを用いた [11]。平均原子量が高い程比誘電率が高く、バンドギャップが小さい傾向であるといえる。しかしながら、バンドギャップが小さいと誘電損失も大きくなることが懸念される。比誘電率が 20 以上であっても、バンドギャップはなるべく大きいものがのぞましい。

図 1-7 平均原子量 vs 比誘電率

図 1-8 平均原子量 vs バンドギャップ

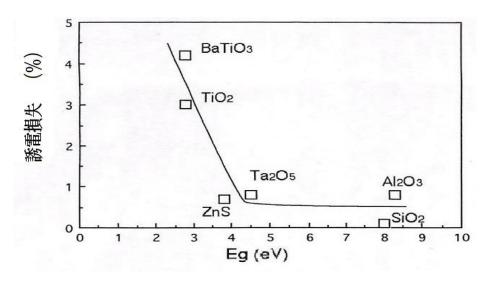

図 1-9 誘電損失 vs バンドギャップ (Eg)

Ta<sub>2</sub>O<sub>5</sub> は比誘電率が 20 以上であるが、バンドギャップも 4 eV 以上となり、この 選択条件に該当する。BST (Ba-Sr-Ti-O 化合物)、STO (Sr-Ti-O 化合物)、PZT (Pb-Zr-Ti-O 化合物)などの 3-4 元化合物のバンドギャップは 3-4 eV と小さい上 に、3元素以上の化合物の元素組成の安定した制御が極めて難しいこともあり、 選択しなかった。これらの酸化物はイオン性酸化物であり、誘電率が高くなるも のの、イオン結合が強いために原子間距離が大きくなるとともに、共有性結合が 弱まり、バンドギャップは減少する。 図 1-9 は誘電損失とバンドギャップの関係 を示している[11]。チタン酸化物は、バンドギャップが比較的小さいこともあ り、誘電損失は大きくなる傾向がある、この関係については、理論的な裏付けは されていないが、バンドギャップが小さいと、ドナー準位などの影響により誘電 損失に影響を与えやすいと考えられる。従来用いられている SiO2、Al2O3 は誘電 損失が1 %以下であるが、誘電率は10以下と小さい。Ta2O5の誘電損失は1 % 以下であるが、比誘電率は20以上の値が報告されている。一方、比誘電率が40 以上となると、バンドギャップは3eV前後となり、誘電損失も大きくなる傾向 と考える。これらの結果から、誘電損失が小さく、比誘電率が20以上で、バン ドギャップは3~6eVの範囲でなるべく大きい材料を選択の指針とできる。TiO2 は比誘電率が高いものの、誘電損失が大きく、組成が複数あるため除いた。この 選択の対象となる安定な金属酸化物としては、ポーリングの電気陰性度の評価 から抽出した材料である Zr、Nb、Hf、Ta、Y から選択できる。このうち、Ta<sub>2</sub>O<sub>5</sub> は 2 元系で組成が安定し、単体のコンデンサー材料として実績があり、誘電率 が 20 以上と高いが、バンドギャップは 4 eV 以上あり、誘電損失が小さいことか ら、最も有望と考えた。Zr、Hf、Nb等の酸化物も可能性のある材料といえるが、 Zr、Hf、Nb 酸化物は Ta<sub>2</sub>O<sub>5</sub>より比誘電率が低く、Ta<sub>2</sub>O<sub>5</sub>に優位性があると判断し た。

#### 1.3 研究開発着手時の高誘電率膜の電気的特性と製造方法のまとめ

# 1.3.1 高誘電率絶縁膜の電気的特性の比較評価

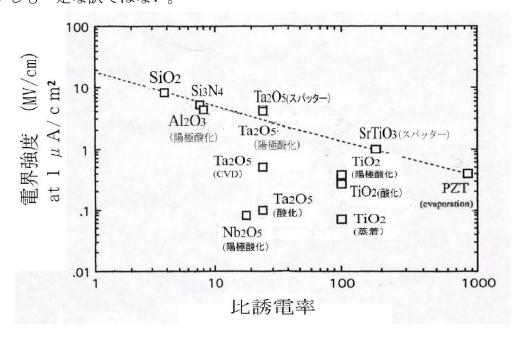

次に、半導体メモリの容量絶縁膜として使う場合には、実使用電圧における蓄積可能な電荷量の評価が必要となる。この値は絶縁破壊に至る寿命が一定期間、例えば、10年保証できる時の最大の蓄積電荷量として求めることができる。また、実使用時の漏洩電流が一定値以下でなければならない。つまり、書き込んだ情報がリーク電流(漏れ電流)により消失しにくいために、十分にリーク電流(漏れ電流)が低いことが必要となる。図 1-10 は絶縁破壊電界強度の大きい材料について、リーク電流が 1  $\mu$ A/cm² となる電界強度と比誘電率の関係をこれまでの文献からまとめたものである。 $Ta_2O_5$ 、 $TiO_2$  に示される様に、形成方法により、電界強度で示される絶縁性は大きく異なることがわかる。 $Nb_2O_5$  を除く材料の最も高い電界強度の比誘電率依存性から、比誘電率の増大とともに電界強度が低下していく傾向があることがわかる。(1-1) 式から算出される様に、蓄えられる蓄積電荷量は電界強度と比誘電率の積( $\epsilon$ ·E)に比例するが、この値は必ずしも一定な訳ではない。

図 1-10 所定のリーク電流となる電界強度 vs 比誘電率

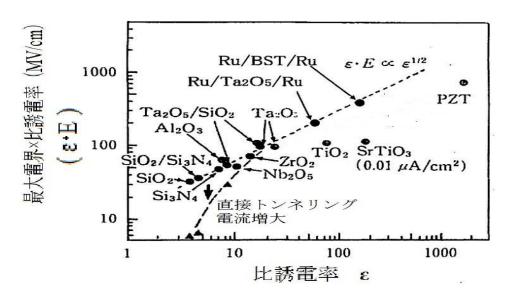

図 1-11 は金属酸化物の文献値、実測値から、最も高い電界強度を用いて( $\epsilon$ ・E) の値と比誘電率の関係をまとめたものである [12]。 $TiO_2$ 、 $Nb_2O_5$  を除いて、誘電率の増加とともにより大きな蓄積電荷量を実現でき、( $\epsilon$ ・E) は近似的に  $\epsilon^{1/2}$  に比例して大きくなる経験則が得られる。従来使われている、 $SiO_2$ ,  $SiO_2$ / $Si_3N_4$  は

図 1-11 最大電界強度・比誘電率 v s 比誘電率、 最大電界強度: リーク電流が 1μA/cm<sup>2</sup> となる電界強度

薄膜化により、直接トンネリング電流が増加して絶縁耐圧に相当する最大電界強度が低下するために、( $\epsilon$ ·E)が低下して、容量としての性能も低下する。  $Ta_2O_5/SiO_2$  膜、Ru 電極間の  $Ta_2O_5$  膜、BST 膜は  $\epsilon^{1/2}$  に比例して( $\epsilon$ ·E)が増加し、高誘電率化によりキャパシタの蓄積電荷量を増加させることができる。本研究では、比誘電率が 20 以上の 2 元系化合物のなかで  $Ta_2O_5$  膜が最も( $\epsilon$ ·E) が大きく、最も有望な材料と考えた。 $TiO_2$ 、 $Nb_2O_5$ 、 $ZrO_2$  は  $Ta_2O_5$  よりも( $\epsilon$ ·E) が小さく、容量絶縁膜としての性能が劣る判断した。 3 元系の BST、PZT の( $\epsilon$ ·E) は  $Ta_2O_5$  膜よりも高いもののバンドギャップが小さく、3 元系以上の化合物の組成の均一性の制御は極めて難しく、製造技術として選択することはできなかった。  $Y_2O_3$ 、 $HfO_2$  等については、研究開発着手段階では、 $Ta_2O_5$  と比較できるデータが少なく、 $Ta_2O_5$  を優先して開発することとした。

#### 1.3.2 Ta<sub>2</sub>O<sub>5</sub> 膜形成方法について

図 1-10 に示される様に高誘電率膜の特性は膜形成方法、形成条件により大きく変化する。本節に、研究開発着手時に報告されていた  $Ta_2O_5$  膜の形成方法について、それぞれの特徴についてまとめる。

#### (1) 陽極酸化方法

電解液中に置かれた Ta は、外部電界によって Ta イオンと電子に解離し、Ta イオンは酸化膜中の準安定な位置に移動して表面に達し、酸素と結合して酸化

物を生ずる。電解液と酸化膜との界面は酸素過剰な P 型層があり、中間が化学量論的には  $Ta_2O_5$  に近い領域となる。また、電解液中の負イオンも酸化膜中に取り込まれ、表面層を P 型層にする。電解液としてリン酸を用いると  $O^2$ -の他に、 $PO_4$  が取り込まれ、酸化膜中に燐も混入する。図 1-10 に示す様に、陽極酸化により形成された比較的厚い膜の絶縁耐圧は良好である場合が多いが、高集積半導体素子において必要とされる薄膜領域で、厚さ方向に均一な膜を形成することは困難である。例えば、整流作用が現れる場合が報告されている [13]。これは、膜厚方向に酸素濃度の変化があるためと考えられる。酸素が不足した酸化タンタル膜は N 型半導体的な性質となり、逆に酸素の多いところは P 型となり、P-I-N 接合が形成されるためと解釈されている。構造的には、下部電極はタンタル、あるいは、タンタル化合物に限定されるうえに、半導体基板を電解液中に設置し、電界を印加できる構造とする必要があり、素子構造を制約する要因が多い。従って、シリコン半導体製造プロセスに適合しにくい形成方法と考えられる。

#### (2) 熱酸化法

金属 Ta 膜をスパッター法により Si 基板上に形成した後、酸素を含む雰囲気中で加熱することにより、 $Ta_2O_5$  膜を形成する [14]。図 1-10 に示す様に、この  $Ta_2O_5$  膜の絶縁耐圧は低く、リーク電流(漏れ電流)は極めて大きい。スパッター法で形成した Ta 膜は多結晶体であり、その表面は結晶粒径程度の凹凸が生じている。電極表面の凸部には、電界集中が起こりやすく、比較的低電界の印加によってもリーク電流が大きくなり、絶縁破壊しやすくなるものと考えられる。リーク電流の少ない 10 nm 前後の薄膜の形成を行うには適さないと考えられる。

#### (3) 反応性スパッター法

反応性スパッターとは、アルゴンと酸素の混合ガス中での高周波プラズマを発生させ、Ta ターゲットをスパッターして  $Ta_2O_5$  膜を形成する方法である[15]。この方法によって形成した  $Ta_2O_5$  膜は、膜が緻密であり、絶縁耐圧が高いなどの優れた特性を持っていることがわかった。ただし、この方法では、膜の堆積は方向性を持っており、凹凸のある基板上に均一な膜を形成するのは難しい。従って、立体化の進んだ DRAM 容量部への適用は困難である。

# (4) CVD 法(CVD: Chemical Vapor Deposition、化学的気相成長)

立体化された素子構造に均一な膜を形成するには、スパッター法よりも良好な段差被覆性を実現可能な CVD 法の開発が重要な課題である。CVD 法としては活性化源として、熱、プラズマ、光を用いるものなどがある。熱 CVD では、タンタルアルコキシドを減圧下で熱分解する方法では、400 ℃前後では十分な

堆積速度が得られるが、スパッター膜と比較して絶縁性が劣るという問題があった [16]。研究開発着手時では、これを改善する方法が提案されている。斉藤らは堆積時に Ti を添加することにより絶縁耐圧が改善されることを示した [17]。また、紫外線を照射した雰囲気において、五塩化タンタルなどのタンタルハロゲン化物やタンタルアルコキシドを 200-300  $\mathbb C$ の低温で光分解により膜形成を行う光 CVD によれば、良好な絶縁耐圧を示す  $Ta_2O_5$  膜を形成することができる [18、19]。光 CVD による  $Ta_2O_5$  膜形成後に、酸素雰囲気において UV 照射をしながら熱処理することにより、絶縁耐圧が改善することが報告された [18]。光 CVD は量産性、プロセス安定性、段差被覆性において課題があり、シリコン半導体素子の製造に適用された例は少ない。プラズマ CVD としては、 $TaCl_5$ , $NO_2$  を用いた形成方法が提案されている [20]。活性な酸素プラズマ雰囲気において、膜形成が行われ、イオンの衝突により膜が緻密化することから、堆積時に良好な絶縁性を得ることができることが報告されている。しかし、反応性スパッター法と同様に、基板面に垂直方向にかかる電界により、段差被覆性に課題がある。

以上に示す方法のほかに、ゾルーゲルなどの方法も適用可能である。本研究では半導体プロセスへの適用という観点より、薄膜で安定した膜形成が期待できる反応性スパッター法と三次元構造の素子に対応するためのCVD法による膜形成方法について検討した。

#### 1.4 本研究の目的と本論文の構成

#### 1.4.1 本研究の目的

1.1.1 節に述べたように、16 メガビット DRAM 以降の高集積化、微細化を進めるにあたって、半導体メモリ用容量絶縁膜として多用されてきた  $SiO_2$ 、 $SiO_2/Si_3N_4$  積層膜のスケーリング則に従う薄膜化は限界に達することがわかった。この限界を超えた  $SiO_2$  換算膜厚で 4 nm から 3 nm 以下の薄膜化を高誘電率容量絶縁膜  $Ta_2O_5$  膜により実現し、16 キロビットバイポーラメモリ素子、64 メガビット DRAM 以降のシリコン半導体メモリ素子の実用化を可能とすることを本研究の目的とする。

#### 1.4.2 本論文の構成

第 1 章では、研究の背景および研究の目的および半導体素子に必要とされる高誘電率容量絶縁膜の材料選択にあたって、種々の高誘電率材料のなかから、

$Ta_2O_5$  膜を選択した理由について議論する。特に、DRAM 素子の 64 メガビット DRAM 以降の高集積化を達成するために、従来の  $SiO_2/Si_3N_4$  積層膜にかわる高 誘電率  $Ta_2O_5$  容量絶縁膜が必要であること、また、立体構造容量部に  $Ta_2O_5$  容量 絶縁膜を形成することが必要であることを説明する。

第2章では、16キロバイポーラメモリ素子のメモリセル縮小のために、高濃度単結晶シリコン基板上に反応性スパッターによる  $Ta_2O_5$  膜を形成する技術について説明する。特に、800  $^{\circ}$   $^{\circ}$  の乾燥酸素熱処理(ウィークスポット酸化結晶化熱処理)により信頼性が顕著に改善された。 $Ta_2O_5$  膜厚が  $70\,\mathrm{nm}$  であると、ウィークスポット酸化結晶化熱処理によりクラックが発生するが、 $10\,\mathrm{nm}$  以下ではクラックは発生せず、リーク電流も増加することなく、欠陥密度が低減し、絶縁破壊信頼性が顕著に向上した。経時的絶縁破壊評価(TDDB)により、 $Ta_2O_5/SiO_2$  三層構造の絶縁破壊寿命は、単層  $SiO_2$  膜の絶縁破壊寿命よりも 5 析優れている。 $SiO_2$  換算膜厚 3-4  $\mathrm{nm}$  の容量絶縁膜を  $Ta_2O_5/SiO_2$  積層構造により実現することができた。

第3章では、DRAM への  $Ta_2O_5$  膜適用の基礎検討として、多結晶シリコン電極上への反応性スパッター法により形成した  $Ta_2O_5$  膜のリーク電流特性、及び、長期信頼性について述べる。多結晶シリコン電極と  $Ta_2O_5$  界面に  $Si_3N_4$  膜を介在させた構造についても比較検討している。従来、多結晶シリコン電極上の熱酸化膜は単結晶シリコン上の熱酸化膜と比較して、大幅な絶縁破壊信頼性の低下がみられるが、 $Ta_2O_5/SiO_2$  積層膜では、 $Ta_2O_5$  膜形成後のウィークスポット酸化結晶化熱処理により、優れた信頼性が得られることが実証できた。また、 $Si_3N_4$  膜を界面に介在させた場合には、絶縁破壊寿命信頼性の面では、 $Ta_2O_5/SiO_2$  積層膜より劣ることがわかった。DRAM 素子へ  $SiO_2$  換算膜厚 3 nm の多結晶シリコン上  $Ta_2O_5/SiO_2$  積層膜を実現できる確信が得られた。

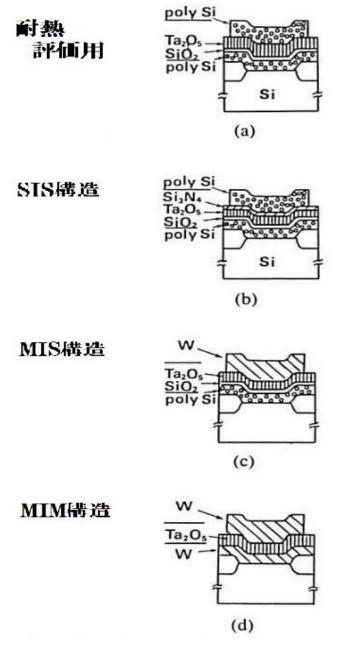

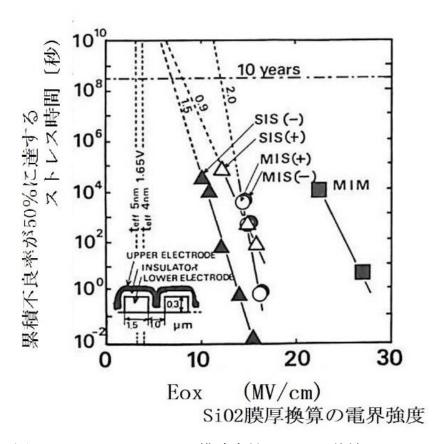

第4章では、DRAM 容量部の構造として、3種の構造について比較検討した。 MIM 構造、MIS 構造、SIS 構造である。高誘電率絶縁膜の特性をより発揮できるのは、金属電極間に  $Ta_2O_5$  膜のみを適用する MIM 構造である。また、第3章にて説明した MIS 構造は  $Ta_2O_5/SiO_2$  積層構造によって、多結晶シリコン上でも良好な長期信頼性が得られ、SiO2 換算膜厚で 3 nm までの容量絶縁膜が得られる。また、プレート電極として、従来の DRAM と同様に多結晶シリコン電極を用いる SIS 構造では、 $Ta_2O_5$  膜上に  $SiO_2$ ,もしくは  $Si_3N_4$  膜からなる反応防止膜が必要となる。これらの構造のリーク電流、及び、絶縁破壊の長期信頼性評価を比較した。MIM 構造はリーク電流の観点から、 $SiO_2$  換算膜厚で 2 nm までの薄膜

化が可能であるが、欠陥密度が多く、信頼性に課題がある。一方、SIS 構造は膜厚の薄膜化にともなって、絶縁破壊の長期信頼性は MIS 構造に劣る上に、SiO<sub>2</sub> 換算膜厚で 3 nm の薄膜化は難しい。従って、64 メガビット DRAM を実現するためには、立体的な容量構造に加えて、 $SiO_2$  換算膜厚 3 nm まで薄膜化できる MIS 構造の  $Ta_2O_5/SiO_2$  積層構造が最も有望である。また SIS 構造を用いて、従来の DRAM プロセスに  $Ta_2O_5$  膜を有する容量絶縁膜を適用した結果、 $Ta_2O_5$  膜を DRAM プロセスに導入しても、デバイス特性を劣化させることはなく、 $Ta_2O_5$  膜を DRAM に適用可能であることを示した。

第5章では、積層容量型メモリセルに  $Ta_2O_5$  膜を適用するために、CVD 法による  $Ta_2O_5$  膜の検討を行った結果について説明する。CVD 法により形成した  $Ta_2O_5$  膜は反応性スパッター法による  $Ta_2O_5$  膜と比較して、リーク電流が大きく、絶縁耐圧が劣る。また、ウィークスポット酸化結晶化熱処理をしても、反応性スパッターによる  $Ta_2O_5$  膜の絶縁耐圧より劣っている。その原因は、CVD 法による  $Ta_2O_5$  膜中に酸素欠陥が多いためと考え、CVD 法により形成した  $Ta_2O_5$  膜に種々の活性な酸素処理を施すことにより、酸素欠陥を低減することを検討した。その結果、UV-O3 処理等の活性酸素処理を行うことにより、大幅にリーク電流が減少するとともに、ウィークスポット酸化結晶化熱処理を行うことにより、反応性スパッター法による  $Ta_2O_5$  膜と遜色のない絶縁破壊信頼性を有する  $Ta_2O_5$  膜を実現することができた。CVD 法による  $Ta_2O_5$  膜と UV-O3 処理とウィークスポット酸化結晶化熱処理との二段階熱処理により、王冠型容量電極表面に良好な被覆性を確保しながら、所定のリーク電流以下となる、 $SiO_2$  換算膜厚  $2.8\,$ nm の容量絶縁膜を実現し、高誘電率容量絶縁膜を有する  $64\,$  メガビット  $DRAM\,$  メモリセルを世界で初めて試作することに成功した。

第6章では反応性スパッター法、および、CVD 法による  $Ta_2O_5$  膜の構造について検討した。結晶性、O/Ta 組成比、酸素の配位数と Ta-O の結合距離について比較評価を行った。反応性スパッターによる  $Ta_2O_5$  膜はウィークスポット酸化結晶化熱処理の有無によらず、酸素の Ta 原子への配位数は T であった。CVD 法による  $Ta_2O_5$  膜にウィークスポット酸化結晶化熱処理を行っても、リーク電流が多いままであり、Ta-O 結合距離の大きく、酸素の配位数は T-6 の結晶となった。この結晶は酸素の欠陥が多いと考えられる。CVD 法による  $Ta_2O_5$  膜に Ta-O 結合距離が小さく、Ta-D が Ta-O を Ta-O を Ta-D を Ta-D

ークスポット酸化結晶化熱処理により生成する結晶化した反応性スパッター法による  $Ta_2O_5$  膜は異なる Ta への酸素配位数、異なる Ta-O 結合距離を示し、結晶構造が異なることがわかった。

第7章では本論文の内容を総括する。

本論文では高誘電率  $Ta_2O_5$  膜のシリコン半導体メモリ素子の容量絶縁膜の適用について報告した。 $Ta_2O_5$  膜の実用化にあたって、CVD 法による  $Ta_2O_5$  膜中の酸素欠陥は活性酸素処理で修復される。一方、CVD 法、反応性スパッター法によらず、絶縁耐圧等の膜特性の均一性、絶縁破壊の長期信頼性はウィークスポット酸化結晶化熱処理により顕著に改善される。これら  $Ta_2O_5$  膜プロセス技術の確立により、16 キロビットバイポーラメモリ素子の製品化を可能とし、更に、二段階熱処理を行った CVD- $Ta_2O_5$  膜を適用することにより、64 メガビット DRAM、256 メガビット DRAM 素子の製品化が可能となった。

また、本論文で示す高誘電率容量絶縁膜と王冠型容量構造の組み合わせは、 現在の DRAM の基本的構成となり、また、本論文で示す高誘電率膜の製造プロ セスは現在のシリコン半導体メモリ素子に適用する高誘電率膜の製造方法の基 本的プロセスとなっており、高誘電率膜の実用化の先駆けとなる研究となった。

# 1.5 参考文献

- [1] R.H.Dennard et al., "Design ofion-implanted MOS-FET's with very small physical dimentions," IEEE J. SSC, vol.9, no.5, p.256, 1974.

- [2] S. Asai, "Trend in megabit DRAMs," in IEDM Tech. Dig., p.368, 1984

- [3] C. Hu, "Thin oxide reliability," in IEDM Tech. Dig., p.368, 1985

- [4] M. Koyanagi, T. Sunami, N, Hashimoto, and M. Ashikawa, "Novel high density stacked capacitor MOSRAM," in IEDM Tech, Dig., p.348, 1978.

- [5] M. Aoki, J. Itoh, S. Kimura, and Y. Kawamoto, "1.5V DRAN for battery-based application," in ISSCC Dig. Papers, p.238 Feb, 1989.

- [6] S. Kimura, Y. Kawamoto, N. Hasegawa, A. Hiraiwa, M. Horiguchi, A. Aoki, T. Kisu, and H. Sunami, "A 5.4 μm² stacked capacitor DRAM cell with 0.6 μm² quadruple-polysilicone-gate technology," in Extended abstract 19<sup>th</sup> Conf. on Solid State Devices and Materials,1987.

- [7] T. Kaga, T. Kure, H. Shinriki, Y. Kawamoto, F. Murai, T. Nishida, Y. Nakagome, D. Hisamoto, T. Kisu, E. Takeda, K. Itoh "Crown-shaped stacked-capacitor cell for 1.5-V operation 64-MbDRAMs" IEEE Trans. Electron Devices, vol. 38, p. 255, 1991.

- [8] H. Shinriki and M. Nakata, "UV-O<sub>3</sub> and Dry-O<sub>2</sub>: Two-Step Annealed Chemical Vapor-Deposited Ta<sub>2</sub>O<sub>5</sub> Films for Storage Dielectrics of 64-Mb DRAM's" IEEE Transactions on Electron Devices Vol.ED-38, No.3, March p.455, 1991.

- [9] H. Watanabe, T. Tatsumi, A. Sakai, N. Aoto, and T. Kajikkawa "An Advanced Technique for Fabricating Hemispherical-grained (HSG) silicon storage electrodes" IEEE Transactions on Electron Devices Vol.ED-42, No.2, February p.295, 1995.

- [10] J. Yugami, T. Mine, S. Iijima, and A. Hiraiwa, "Inter-poly SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> capacitor films 5 nm thick for deep submicron LSIs," in Extended abstract 20<sup>th</sup> Conf. on Solid State Devices and Materials, (Tokyo, 1989) p.173.

- [11] P. J. Harrop and D. S. Campbell "Selection of Thin Film Capacitor Dielectrics "Thin Solid Films, 2. p.273 (1968).

- [12] 神力 博:応用物理 第60巻、第11号 (1991) "高誘電率材料のLSI 容量絶縁膜への応用"

- [13] S. M. Gubanski and D. M. Hughes "Conduction Process in Anodic Ta Oxide Thin Films with Gold Counter electrode" Thin Solid Films, 52 (1978) p.119.

- [14] D. J. Smith and L. Young "Optical and Electrical Properties of Thermal Tantalum Oxide Films on Si" IEEE Transaction on Electron Devices vol.ED-28, No.1 (1981) p.22.

- [15] P. L. Young "DC Electrical Conduction in Thin Ta<sub>2</sub>O<sub>5</sub> Films, Bulk Limited Conduction" J. Apply. Phys. Vol.47, No.1, Jan, (1976) p.235.

- [16] E. Kaplan, M. Balog and D. Frohman-Bentchkowsky "Chemical Vapor Deposition of Tantalum Pentoxide Films for Metal-Insulator-Semiconductor Devices" J. Electrochem. Soc. Vol.123, No.10, (1976) p.1570.

- [17] M. Saitoh, T. Mori and H. Tamura "Electrical Properties of thin Ta<sub>2</sub>O<sub>5</sub> films grown by Chemical Vapor Deposition" in IEDM Tech. Dig., p.680, 1986.

- [18] K. Yamagishi and Y. Tarui "Photo-CVD of Tantalum Oxide Film from Pentamethoxy Tantalum for VLSI Dynamic Memories" Jpn. J. Appl. Phys. Vol.25 1986, L306.

- [19] M. Matui, S. Oka, K. Yamagishi, K. Kuroiwa and Y. Tarui "Photo-process of tantalum oxide films and their characteristics" Jpn. J. Appl. Phys. 27. P.506, (1988).

- [20] Y. Numasawa, S. Kamiyama, M. Senke and M. Sakamoto "Ta<sub>2</sub>O<sub>5</sub> plasma CVD technology for DRAM stacked capacitors" in IEDM Tech Dig., 1989, p.43.

# 第 2 章 反応性スパッター法による Ta<sub>2</sub>O<sub>5</sub> 膜の電気的特性、信頼性 評価とバイポーラメモリ素子用容量絶縁膜への適用

# 2.1 緒言

Si の半導体素子の高集積化とともに、Si 半導体メモリ素子に適用されてきた SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> 積層膜からなる容量絶縁膜はスケーリング則に従って薄膜化すると、漏れ電流が急増してしまう物理的限界に達する [1], [2]。このため、この物理的限界を克服するために、これらの容量絶縁膜を高誘電率誘電体に置き換えることを提案した [3]。とりわけ、最も高集積なメモリ素子である DRAM に高誘電率容量絶縁膜を適用することをめざして、 $Ta_2O_5$  膜を選択し、DRAM への適用について報告した [4]。極めて高い信頼性を必要とする DRAM に適用するには、下記の課題を解決する必要があった。

第一の課題:  $Ta_2O_5$  膜は 600  $^{\circ}$ C以上の熱処理により、絶縁耐圧が低下することが報告され、通常の DRAM プロセスで必要とされる 800  $^{\circ}$ C以上のプロセスへの適用が懸念される。

第二の課題: 64 メガビット以降の DRAM では  $SiO_2$  換算膜厚 3 nm 以下に相当する高い容量を確保するために、 $Ta_2O_5$  膜の膜厚を 10 nm 以下とする必要があるが、薄膜化による信頼性の低下か懸念される。

本章では、16 キロビットバイポーラメモリ素子用容量絶縁膜への  $Ta_2O_5$  膜の適用を検討するなかで、800  $^{\circ}$   $^{\circ}$

#### 2.2 高速バイポーラメモリ素子用高容量キャパシタ(容量素子)の必要性

# 2.2.1 ソフトエラー対策の動向

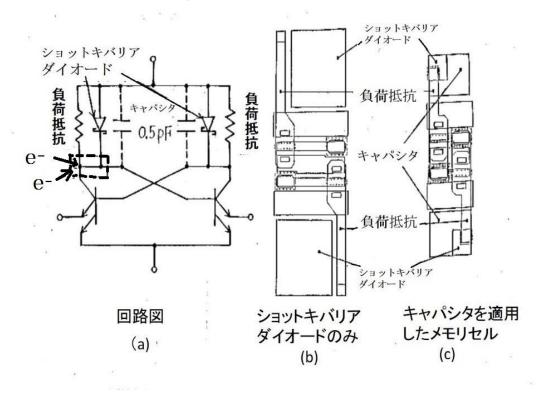

高速バイポーラメモリ素子では、その高集積化、高速化に伴うトランジスタの面積の縮小などによって浮遊容量が著しく減少し、その結果、図 2-1 (a) の回路図に示すような互いに交差接続されたトランジスタよりなるフリップフロップ回路のベース・コレクタ接続領域(点線で囲む領域)に α線によって発生した負

電荷が流入した場合には、ベース電位が変動してフリップフロップ回路に保持 された情報が反転し、意図しない情報の書き換えが起きるという問題があった。 1.1 節に示す DRAM におけるソフトエラーと同様に、この  $\alpha$  線による情報の意 図しない書き換えもソフトエラーに該当する。この対策として、図 2-1 (a)の 中の破線で示すキャパシタを負荷回路に並列に接続し、信号雑音電流を吸収す ることが考案された。従来の高速バイポーラメモリ (図 2-2 参照:HM2142, HM2144 )では、図 2-1 (b) に示すようなフリップフロップ型メモリセルの情 報書き込みを高速化するために、負荷切り替え用の PtSi 接合によるショットキ バリアダイオードを用いた。このショットキーバリアダイオードのメモリセル に占める面積の割合は約半分となっており、これに付随した接合容量がソフト エラーを防止する効果を持っていた。ところが、メモリセル面積をさらに縮小し、 高速化を図るためにはショットキーバリアダイオードの面積を縮小する必要が あり、必然的にソフトエラー防止用の接合容量が不足してくる。そこで、図 2-1 (c)に示すように、Pd₂Si 接合による小面積のショットキーバリアダイオード と小面積で高容量のキャパシタとの組み合わせにより、メモリセル全体の面積 を縮小し、4倍の高集積化を達成しながら、ソフトエラーを防止できるだけの容 量を確保することができる。

図 2-1 高速バイポーラメモリセルの回路図と面積比較

# 2.2.2 16 キロビット高速バイポーラメモリ素子用容量絶縁膜への要求仕様

大型計算機用 16 キロビット高速バイポーラメモリ素子に  $Ta_2O_5$  膜を容量絶縁膜として用いたキャパシタ(容量素子)を適用することを検討するにあたり、容量絶縁膜としての  $Ta_2O_5$  膜に要求される特性を示す。

# 要求性能

- (1) 単位容量: 7.5 fF/μm<sup>2</sup>以上(SiO<sub>2</sub>換算膜厚: 4.5 nm 以下)、 メモリセル面積が 700 μm<sup>2</sup>以下

- (2) 欠陥密度: <10 cm<sup>-2</sup>以下: 16 キロビットメモリセル (32600 個) のキャパシタの歩留まり 99 %以上

- (3) 高周波特性: 300 MHz まで容量一定 (アクセス時間 5 nsec 以下)

- (4) リーク電流:動作時(0.5 V) < 0.02 A/cm<sup>2</sup>

- (5) 絶縁耐圧 2 V 以上:動作電圧 0.5 V の 4 倍のマージン

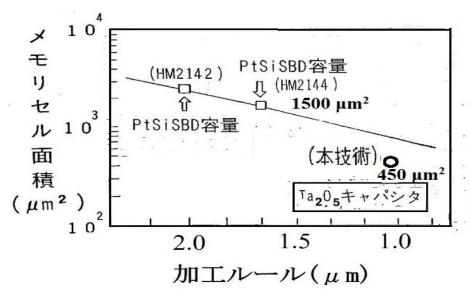

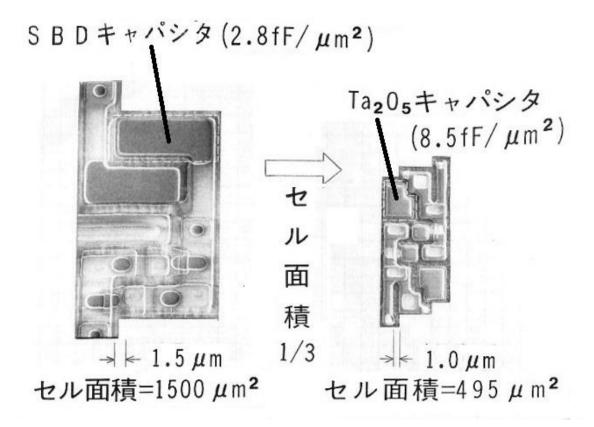

図 2-2 に高速バイポーラメモリセル面積の推移を示す。加工ルールが 1  $\mu$ m となり、セルサイズが 1500  $\mu$ m<sup>2</sup> から縮小されるが、PtSi ダイオードのみを用いる場合には、ソフトエラーを防止するのに必要な容量を確保するためには、 900  $\mu$ m<sup>2</sup> のセルサイズが必要となる。小面積の  $Pd_2Si$  ダイオードと小面積キャパシタ(単位容量 7.5  $tF/\mu$ m<sup>2</sup> 以上)が実現できれば、メモリセル面積を目標の 700  $\mu$ m<sup>2</sup> 以下にできる。本研究では、目標の単位容量より大きな単位容量を有するキ

図 2-2 メモリセスサイズの推移

ャパシタの形成により、 $450 \mu m^2$  と 3 分の 1 に縮小することができた。

メモリセル面積を縮小するために、より小面積のキャパシタでソフトエラーを防止できる容量を確保する必要がある。当初の目標である SiO<sub>2</sub> 換算膜厚 4.5 nm から 4.0 nm 以下まで薄膜化することにより、メモリセル面積を目標より大幅に縮小することが可能となった。一方、単層の SiO<sub>2</sub> 膜では、薄膜化にともないリーク電流が増加するだけでなく、欠陥密度も増加するという課題があった。高誘電率容量膜を適用することによりリーク電流の増加を防止しながら SiO<sub>2</sub> 換算膜厚で 4 nm 以下まで薄膜化しても、製品適用可能な高い信頼性を確保できるか、また、Si 半導体プロセスとの整合性に支障がないか、検証する必要があった。

# 2.3 形成方法

# 2.3.1 反応性スパッター法による Ta<sub>2</sub>O<sub>5</sub> 膜の形成

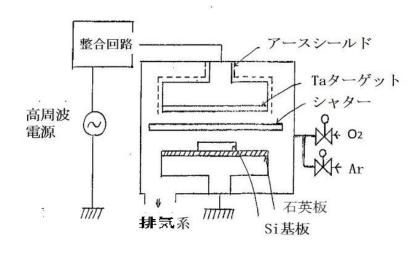

$Ta_2O_5$  膜の形成は、金属の Ta ターゲットを用い、アルゴンと酸素の混合雰囲気中で反応性スパッターを行った。図 2-3 は反応性スパッター装置の断面模式図である。Ta ターゲットの純度は 99.9 %であった。スパッター室はクライオポンプ、オイルフリーターボ分子ポンプ、メカニカルブースタポンプにより排気される。シリコン基板を RCA 洗浄した後、シリコン基板をスパッター装置の基板ホルダー上に設置する。基板の加熱、冷却は行わない。 $6.8 \times 10^{-5}$  Pa  $(5 \times 10^{-7}$  torr) となるまで真空排気を行い、次に、Ar  $/10\%O_2$  混合ガスを導入し、0.68 Pa  $(5 \times 10^{-3}$  torr)となるように導入する。次に、高周波電源を印加して、約1分間プレ放電を行った後、基板を遮蔽するシャッターを開き、 $Ta_2O_5$  膜の成膜を行った後、 $6.8 \times 10^{-5}$  Pa  $(5 \times 10^{-7}$  torr)となるまで真空排気を行い、変素ガスによりチャ

図 2-3 反応性スパッター装置

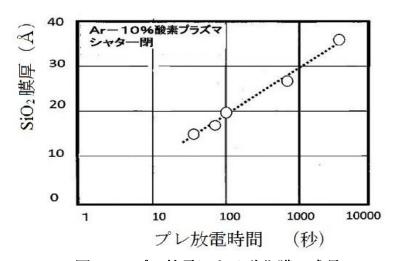

ンバをリークして基板を取り出した。 $Ta_2O_5$  膜の成長速度は $6\,nm$ /分とした。Si 基板の抵抗率は $0.03\,\Omega$ ・cm 以下のものを用い、Si 基板をフッ酸洗浄により自然酸化膜を除去した後、 $Ta_2O_5$  膜を成膜した。図 2-4 はプレ放電の際に形成する $SiO_2$  膜の膜厚の時間依存性である。プレ放電時間とともに、酸化膜厚は増加する。30 秒から 100 秒に増加すると、酸化膜厚は 15 Åから 20 Åと 5 Å増加する。本研究ではプレ放電時間は 60 秒と一定とし、界面に形成される $SiO_2$  膜の膜厚は 18-19 Å 程度となる

図 2-4 プレ放電による酸化膜の成長

# 2.3.2 CVD 法による Ta<sub>2</sub>O<sub>5</sub> 膜の形成

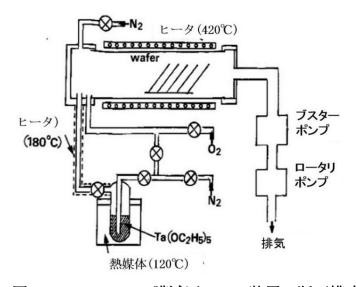

図 2-5 は減圧CVD装置の概略を示す。 $Ta_2O_5$ 膜はテルサムコ製減圧CVD装

図 2-5 CVD-Ta<sub>2</sub>O<sub>5</sub> 膜減圧CVD装置の断面模式図

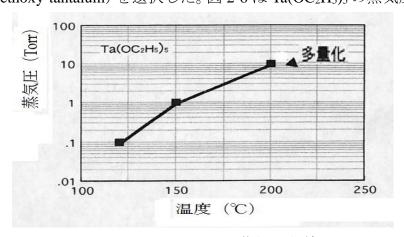

置を用いて形成した [10]。均熱炉中の石英管の両端を O リングシールによるフランジにより真空を保持している。真空排気は回転ポンプとルーツポンプにより排気している。圧力はバラトロン圧力センサーからの圧力をモニターし、自動圧力制御バルブを駆動することにより制御している。温度制御は炉体と石英管の間に設置された熱電対を用いて制御した。制御は 3 領域に分割されたヒーターを独立に制御することにより行った。また、成膜前に予め、石英管内に直接熱電対を導入することにより測定した温度を基準としてそれぞれのヒーター出力を決定している。基板はシリコン基板であり、石英治具に斜めに立てて置き、膜を形成する面を下方に向けてあり、真空排気、真空リークの際の微小なパーティクルの付着を防止した。酸化タンタル膜の原料としては、被覆性に優れた酸化タンタル膜が形成できることと、常温、常圧で液体であり、アルコキシドとしては蒸気圧が高く、取り扱いが容易という理由から Ta(OC2H5)5 (純度 99.9999 %) (Penta-ethoxy-tantalum)を選択した。図 2-6 は Ta(OC2H5)5 の蒸気圧曲線を示す。

図 2-6 Ta(OC<sub>2</sub>H<sub>5</sub>)<sub>5</sub> の蒸気圧曲線

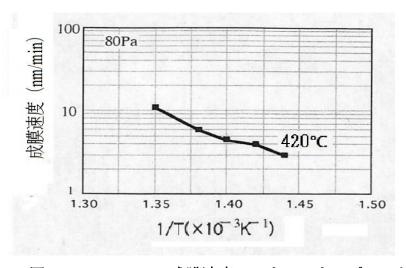

図 2-7 CVD-Ta<sub>2</sub>O<sub>5</sub> 成膜速度のアウレニウスプロット

蒸気圧は継続的に高温に保持していると、次第に低下する傾向があった。これは原料が単量体から多量体に変化するためとわかり、140 ℃で安定して窒素ガスにより気化供給することにより、安定して供給が可能となった。その後、気化装置を用いることにより、液体原料タンク自体を加熱する必要がなくなり、140 ℃以上の気化温度も使用できるようになった。気化ガスは 180 ℃に加熱されたガス配管を通じて反応管に供給された。同時に酸素ガスを供給し、熱分解により膜形成を行う。図 2-7 は成膜速度のアウレニウスプロットを示している(成膜速度の1/T 依存性、T: 成膜温度(K))。成膜温度は420 ℃とした。420 ℃は表面反応律速領域であって、良好な被覆性を得るためには有利である。全ガス圧力は80 Pa とした。

# 2.3.3 Ta<sub>2</sub>O<sub>5</sub> キャパシタの形成方法

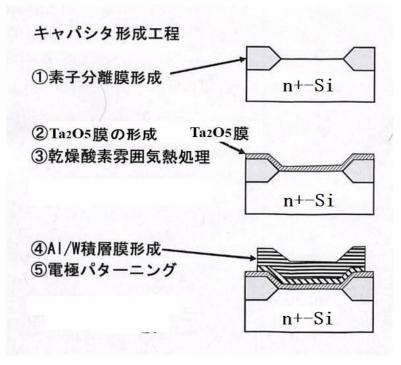

$Ta_2O_5$  膜を容量絶縁膜とするキャパシタ(容量素子)を  $Ta_2O_5$  キャパシタと記載する。電気的特性評価に用いた  $Ta_2O_5$  キャパシタの形成行程を図 2-8 に示す。まず、① 通常の MOS 製造工程により LOCOS 分離絶縁層を形成し、RCA 洗浄を施した後、② 反応性スパッター法、C V D法で  $Ta_2O_5$  膜を形成し、③ 石英加熱炉により、乾燥酸素雰囲気で熱処理する。熱処理温度は 400-1000 ℃であった。④ W ( 100 nm )、Al ( 0.9  $\mu$ m )の順でスパッター法により形成し、⑤ウェットエッチングにより電極加工を行った。

図 2-8 Ta<sub>2</sub>O<sub>5</sub> キャパシタ形成工程

# 2.4 評価方法

# 2.4.1 Ta<sub>2</sub>O<sub>5</sub> 膜の物理分析評価

- ① 透過電子顕微鏡 (TEM: Transmission Electron Microscope): Ta<sub>2</sub>O<sub>5</sub> 膜の断面 形状を透過電子顕微鏡により評価した。加速電圧は 100 KV とした。

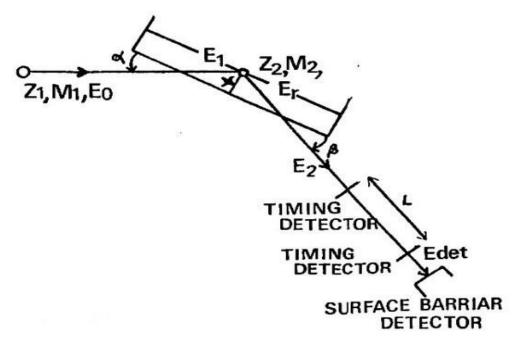

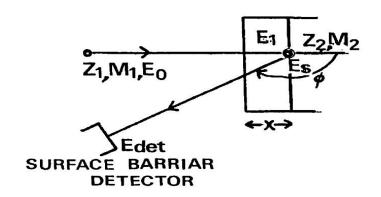

- ② 微小角入射 X 線回折 (XRD: X-ray Diffraction):極薄 Ta<sub>2</sub>O<sub>5</sub> 膜結晶性評価

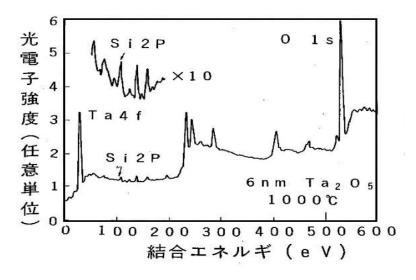

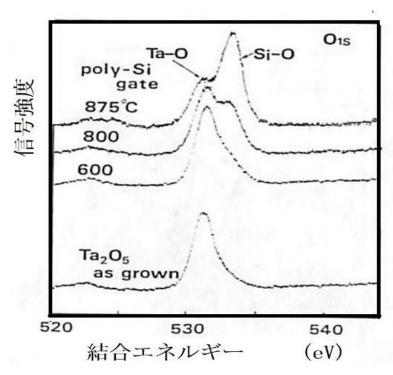

- ③ 光電子分光法(XPS: X-ray Photoelectron Spectroscopy)による評価:熱処理前後の Ta<sub>2</sub>O<sub>5</sub> 膜の化学結合について評価した。Ta<sub>2</sub>O<sub>5</sub> 膜の熱処理前後の化学量論比の変化は、Ta(4f)、O(1s)のピーク高さの比によって評価し、Taピークの化学シフトも評価した。

- ④ 膜厚の評価:エリプソメトリーにより評価した。

- ⑤ 原子間力顕微鏡(AFM: Atomic Force Microscope )による評価: 熱処理前後の Ta<sub>2</sub>O<sub>5</sub> 膜の表面凹凸の変化を評価。

# 2.4.2 Ta<sub>2</sub>O<sub>5</sub> キャパシタの電気的特性評価

- 容量測定:容量はYHP4062測定システムで測定した。周波数は1MHzまたは100KHzで行った。

- ② 容量の高周波特性の測定: YHP4193 ベクトル・インピーダンスメータにより容量と位相角を測定した。測定周波数範囲 800 KHz から 800 MHz の間であるが、測定精度上の問題から 1)800 KHz から 100 MH z と 2)100 MHz から 800 MHz の二つの範囲に分けて測定した。

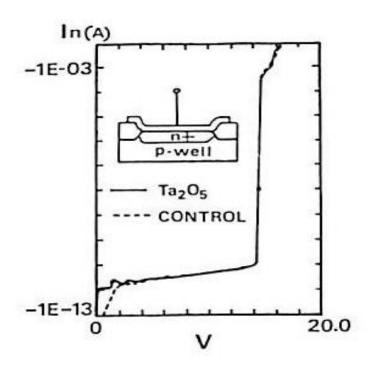

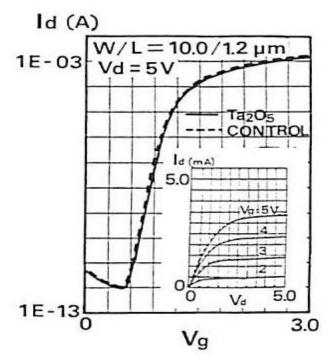

- ③ 電流-電圧特性: YHP4062 測定システムで測定した。電圧は Si 基板が n型 であるので、ゲート電極に正電圧を印加し、順方向の電流-電圧特性を測定した。

- ④ 耐圧ヒストグラム: YHP4062 測定システムとオートプローバによって測定した。耐圧の定義は  $10^{-8}$  A/cm<sup>2</sup> のリーク電流を生ずる電圧とし、耐圧が 1 V 以下のものを欠陥のあるキャパシタとした。電圧の印加速度は 0.1 または 0.3 V/sec であり、変位電流が  $10^{-6}$  A/cm<sup>2</sup> を超えない範囲とした。

- ⑤ TDDB 特性評価:オートプローバにより、定電圧ストレスによる経時的絶縁破壊時間、経時的絶縁破壊時間のヒストグラムを測定。

# 2.5 反応性スパッターTa<sub>2</sub>O<sub>5</sub>膜の基礎特性

この節では、主に反応性スパッターTa<sub>2</sub>O<sub>5</sub>膜の基礎特性に関して述べる。

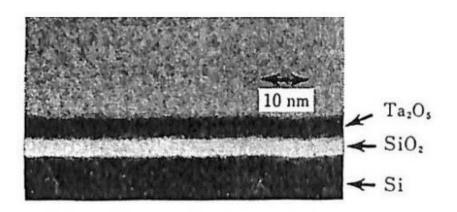

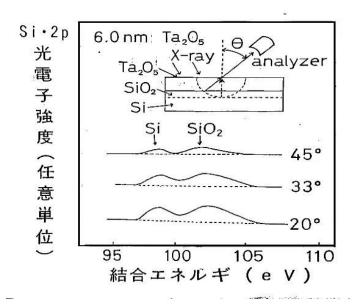

#### 2.5.1 界面酸化膜

$Ta_2O_5$  膜は Si 基板上に形成する場合に問題となるのは、 $Ta_2O_5$  と Si の界面に比誘電率の小さい  $SiO_2$  膜(比誘電率  $ε_s=3.8$ )が形成されることである。図 2-9 は。反応性スパッター法によって形成した 6 nm の  $Ta_2O_5$  膜の断面の透過電子顕微鏡(以下、断面 TEM)写真である。 $Ta_2O_5$  膜形成後に乾燥酸素雰囲気で 1000  $^{\circ}$  の熱処理をすることにより、 $Ta_2O_5$  膜と Si 基板の界面に 6 nm の  $SiO_2$  膜が成長することを示している。図 2-10 は同じ試料を光電子分光( XPS )により測定したスペクトルである。結合エネルギーが 100 eV 近傍において  $Si_{2P}$  ピークが観測されている。このピークが  $Ta_2O_5$  膜の深さ方向のどこに存在するかを調べる目的で、図 2-11 に示すように、光電子アナライザーの角度を変えて  $Si_{2P}$  ピークの膜厚方向の分布を観測した。酸素と結合している  $Si_{2P}$  ピークと酸素と結合していない  $Si_{2P}$  ピークがともに、アナライザーの角表示  $\theta$  が小さくなるにつれて増

図 2-9 Si 基板上 Ta<sub>2</sub>O<sub>5</sub> 膜の断面 T E M写真

図 2-10 Si 上 Ta<sub>2</sub>O<sub>5</sub> 膜の光電子スペクトラム

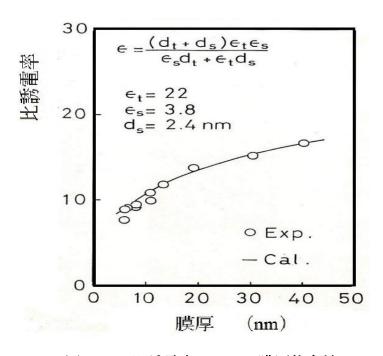

加している。従って、酸素と結合する  $Si_{2p}$  ピークは  $Ta_2O_5/Si$  界面に存在する  $SiO_2$  からの信号であることがわかる。この  $SiO_2$  膜は  $Ta_2O_5$  膜の電気的特性に大きな影響を及ぼすことがわかった。図 2-12 は、比誘電率の  $Ta_2O_5$  膜厚依存性を示す。比誘電率は、膜厚とともに減少してしまう。これは、薄膜領域においては  $Ta_2O_5$  膜の下地の  $SiO_2$  膜の影響が現れるためと考えられる。図中の実線は比誘電率が 22 の  $Ta_2O_5$  膜と比誘電率が 3.8 の  $SiO_2$  膜とが積層しているとして計算したものである。

図 2-11 Si<sub>2p</sub> スペクトラムのアナライザー角度依存性

図 2-12 比誘電率の Ta<sub>2</sub>O<sub>5</sub> 膜厚依存性

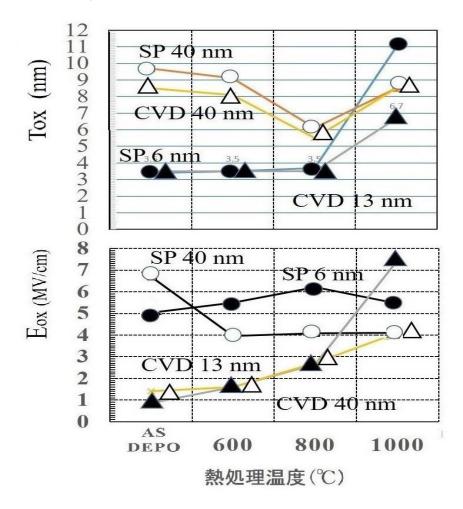

#### 2.5.2 熱的安定性

反応性スパッター法("SP"で示す)、CVD 法("CVD"で示す)により形成した  $Ta_2O_5$  膜は堆積直後では非晶質構造であるが、約 700 ℃で結晶化することが報告されている [11]。熱処理温度によって、 $SiO_2$  換算膜厚での絶縁電界強度 Eox と  $SiO_2$  換算膜厚 Tox がどのように変化するかについて調べた。 $SiO_2$  換算膜厚での絶縁電界強度 Eox は (1-6) 式に従って、 $10^{-6}$  A/cm² のリーク電流となる印加電圧と  $SiO_2$  換算膜厚 Tox より算出して求められる。(1-4) 式に示すように、容量は  $SiO_2$  換算膜厚 Tox に反比例するので、容量の大小は Tox の大小で比較できる。図 2-13 は乾燥酸素雰囲気中での熱処理によって生じる Eox と

図 2-13 スパッター、CVD-Ta<sub>2</sub>O<sub>5</sub> 膜の Eox と SiO<sub>2</sub> 換算膜厚 Tox の乾燥酸素雰囲での熱処理温度依存性

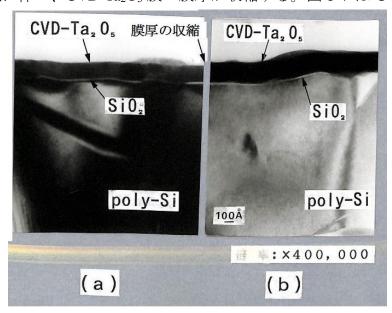

SiO<sub>2</sub> 換算膜厚 Tox の熱処理温度依存性を示している。20 nm より薄膜領域において、スパッター膜と CVD 膜の膜厚は、得られる容量( Tox=3.5 nm )が同じとなるように膜厚を選択しており、それぞれ 6 nm、13 nm であった。CVD 膜は堆積時にポーラスな膜であり、堆積時には膜厚が 13 nm と測定されるものの、熱処理により大きく収縮する。一方、スパッター膜の界面  $SiO_2$  膜厚が成膜時のプラズマ酸化により CVD 膜の界面  $SiO_2$  膜厚より厚くなるために、逆に、スパッターによる  $Ta_2O_5$  膜の膜厚は CVD 膜より薄膜となる。

しかしながら、スパッター膜、CVD 膜とも同等の容量となるようにしたにもかかわらず、CVD 膜の Eox はスパッター膜の Eox に比べて低い。本章で適用対象とするバイポーラメモリ素子では、図 2-1 に示す様に、高濃度 Si 基板上に平面構造の容量部を用いているので、スパッター法で形成しても、被覆性の問題がないことから、スパッター膜によりシリコン半導体素子製品適用の検討を進めることとした。

2.1 節にて、 $Ta_2O_5$  膜の第一の課題として示したように、600  $^{\circ}$   $^{\circ}$   $^{\circ}$  以上の熱処理により、Eox が低下するという問題がある。図 2-13 に示す様に、膜厚が  $40\,\mathrm{nm}$  の  $Ta_2O_5$  膜には、その現象が確認できる。 $40\,\mathrm{nm}$  のスパッター膜は 600  $^{\circ}$   $^{\circ}$   $^{\circ}$  の熱処理で Eox が低下している。一方、 $SiO_2$  換算膜厚 Tox は、600  $^{\circ}$   $^{\circ}$   $^{\circ}$  では大きな変化はないが、800  $^{\circ}$   $^{$

6 nm のスパッター膜の  $SiO_2$  換算膜厚 Tox は熱処理なし、 $600 \, ^{\circ} \! ^{\circ} \! ^{\circ} \! ^{\circ}$  処理によっても殆ど変化がない。一方、Eox は  $600 \, ^{\circ} \! ^{\circ} \! ^{\circ} \! ^{\circ} \! ^{\circ}$  で最大の Eox が得られる。従って、2.1 節で した耐熱性に対する懸念は、薄膜領域では問題とならず、 $800 \, ^{\circ} \! ^{\circ} \!$

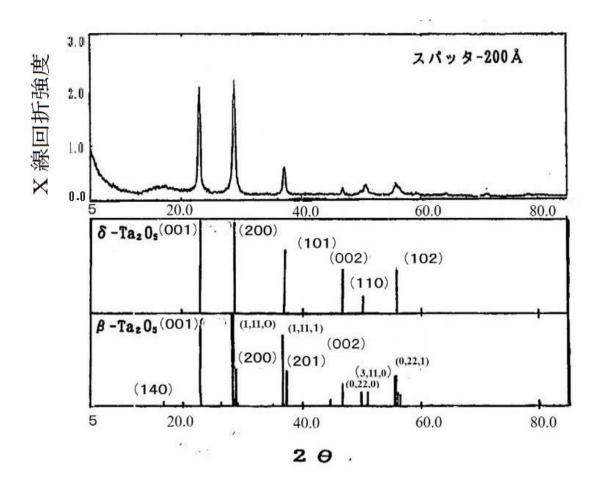

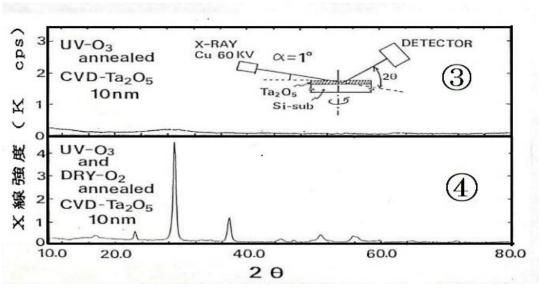

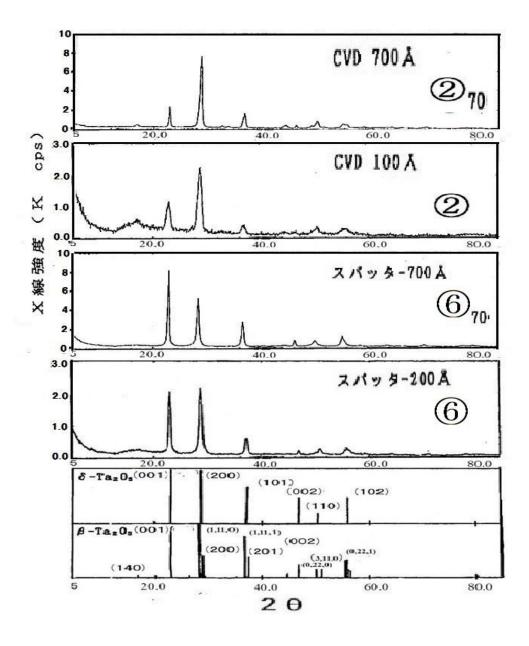

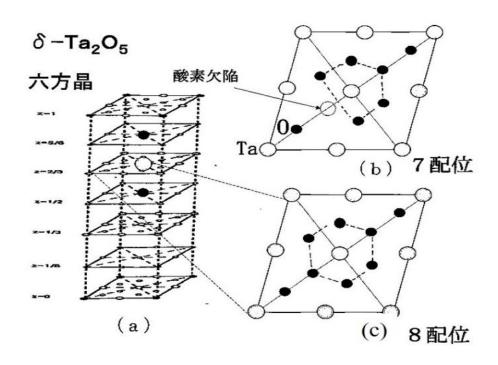

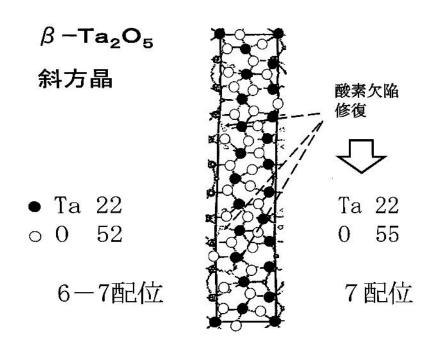

薄膜領域において、容量を減少させることなく、絶縁耐圧が改善される要因について検討するために、薄膜領域における、800  $\mathbb C$ の乾燥酸素熱処理後の結晶化の有無について評価した。微小角入射 X 線回折によって、800  $\mathbb C$ の乾燥酸素雰囲気での熱処理を行った反応性スパッター法による 20 nm の  $Ta_2O_5$  膜を評価した。図 2-14 に示すように、800  $\mathbb C$ の乾燥酸素雰囲気での熱処理により、熱処理なしの場合には観察されない回折スペクトルが測定され、結晶化することが確認できた。 $\alpha$ - $Ta_2O_5$  構造と  $\beta$ - $Ta_2O_5$  構造の主な回折線は 28.3、36.7、50°の近傍にあり、 $\alpha$ - $Ta_2O_5$  構造の六方晶の回折線に対して, $\beta$ - $Ta_2O_5$  構造の斜方晶の回折線は、それぞれの位置に複数の回折を含むという違いがあるものの、この測定から、

図 2-14 乾燥酸素熱処理後の Ta2O5 膜の X 線回折スペクトル

800  $\mathbb{C}$ の乾燥酸素雰囲気での熱処理を行った薄膜領域の  $Ta_2O_5$  膜は  $\alpha$ - $Ta_2O_5$  構造か  $\beta$ - $Ta_2O_5$  構造のいずれかの結晶構造と考えられる。

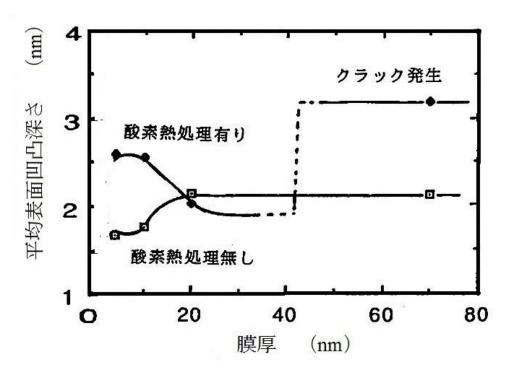

図 2-15 は膜厚 4、10、20、70 nm o  $Ta_2O_5$  膜について、熱処理前後による表面の平均凹凸深さ(nm)の変化を AFM により評価した結果である。800  $^{\circ}$  の乾燥酸素熱処理により、膜厚 70 nm では凹凸深さが急激に大きくなり、クラックの発生に対応する。一方、20 nm では、熱処理後でも凹凸深さの変化はみられず、クラックの発生はないと判断できる。一方、膜厚 4 nm、10 nm の領域では、熱処理により平均凹凸深さが増加することが観察された。10 nm 以下の薄膜領域において、800  $^{\circ}$  の乾燥酸素熱処理に伴う、凹凸の生成があると考えられる。

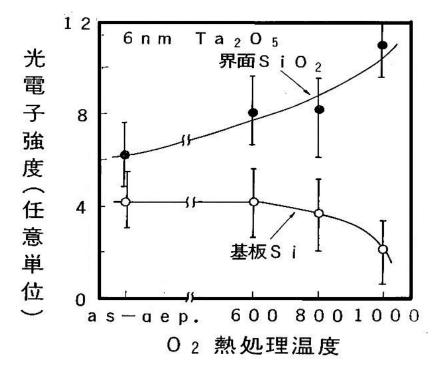

図 2-16 は  $Ta_2O_5$  と Si 界面の  $SiO_2$  膜に起因する  $Si_{2p}$  ピークを、乾燥酸素熱処理温度を変えて測定した結果である。熱処理温度が高くなるとともに、界面  $SiO_2$  のピークは大きくなり、逆に基板からの Si のピークは小さくなる。従って、 $Ta_2O_5$  と Si 界面の  $SiO_2$  膜が成長することがわかる。図 2-17 に、乾燥酸素中で熱処理

図 2-15 AFM 乾燥により酸素熱処理理前後の表面凹凸深さ変化

図 2-16 XPS による Ta<sub>2</sub>O<sub>5</sub>/Si 界面の SiO<sub>2</sub> 膜成長の分析

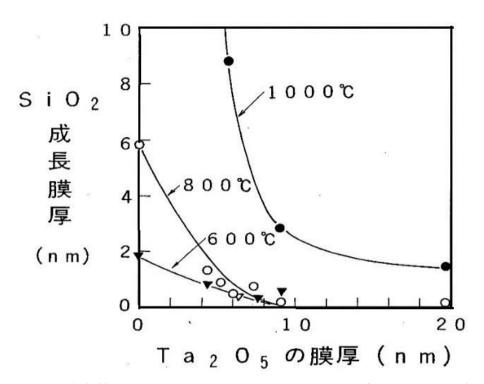

を行った際の容量値の変化から、 $Ta_2O_5$  膜の下地に成長する  $SiO_2$  の膜厚の  $Ta_2O_5$  膜厚、乾燥酸素熱処理温度の依存性を求めた結果を示している。 $Ta_2O_5$  膜厚が 10

図 2-17 乾燥酸素熱処理による Ta<sub>2</sub>O<sub>5</sub>/Si 界面の SiO<sub>2</sub> の成長の Ta<sub>2</sub>O<sub>5</sub> 膜厚依存性

nm 以下の領域では、800  $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$  の熱処理により界面に  $SiO_2$  膜が成長する。一方、10 nm 以上の膜厚の  $Ta_2O_5$  膜と Si 基板界面では、殆ど  $SiO_2$  膜の成長はおきない。 AFM により 10 nm 以下の膜厚領域で観察される凹凸の生成は界面における  $SiO_2$  膜の成長によるものと考えられる。

以上のように、10 nm 以下の  $\text{Ta}_2\text{O}_5$  膜が  $800 ^{\circ}$  の高温熱処理によっても、絶縁耐圧の低下がないことは、10 nm 以下の  $\text{Ta}_2\text{O}_5$  膜を容量絶縁膜形成後に高温プロセスを必要とする DRAM に適用できることを確信させる結果となった。

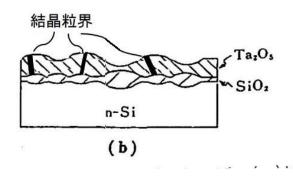

### 2.5.3 ウィークスポット酸化結晶化モデル

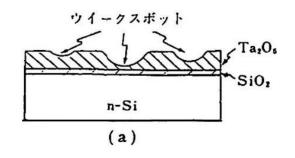

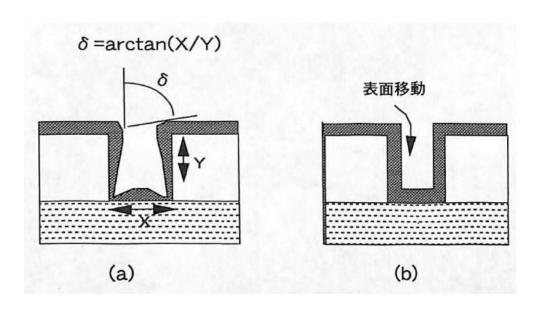

図 2-17 に示したように、10 nm 以下の  $Ta_2O_5$  膜においては、800 C の乾燥酸素中の熱処理によって、 $Ta_2O_5$  膜の膜厚が薄い場所ほど界面により厚い  $SiO_2$  膜が成長することがわかった。例えば、 $Ta_2O_5$  膜厚が局所的に薄くなるような欠陥部の下地の Si が選択的に酸化されることが推定できる。しかしながら、図 2-15 に示す AFM の結果は、 $Ta_2O_5$  膜表面の凹凸の変化が、広い範囲で均一に起きる現象であることから、結晶化の際に生成する微小なピンホールや結晶粒界を介して界面が酸化され、 $SiO_2$  膜が形成されたと考えられる。従って、図 2-18 に示すすような欠陥部分の修復モデルを考えている。つまり、図 2-18 (a) に示す様な、

図 2-18 ウィークスポット酸化結晶化モデル

絶縁耐圧が低くなりやすい局所的に膜厚が薄い部分が存在し、乾燥酸素雰囲気での熱処理により、界面に SiO<sub>2</sub> 膜が形成される。一方、乾燥酸素雰囲気での熱処理により、結晶化と同時にピンホールや結晶粒界が生成し、その下地界面に SiO<sub>2</sub> 膜が形成されることも推測できる。AFM の結果は、凹凸が広い範囲で均一に生成されることを示唆している。従って、図 2-18 (b) に示す様に、局所的に 膜厚が薄い部分に加えて、結晶化の際にピンホールや結晶粒界が生成される部分でも界面酸化が進むものと考える。この処理方法をウィークスポット酸化結晶化処理と呼ぶこととする。

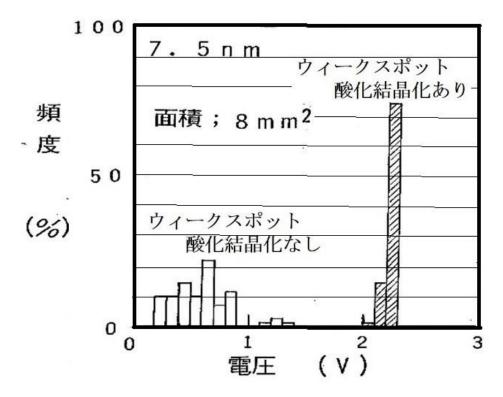

図 2-19 は  $Ta_2O_5$  膜厚 7.5 nm のキャパシタ(面積 8 mm²、個数  $100 \, \gamma$ )におけるリーク電流が  $10^{-6}$  A/cm² となる初期耐圧ヒストグラムを示している。 800 ℃の乾燥酸素熱処理であるウィークスポット酸化結晶化熱処理を行うことにより、大面積でも良好な電流一電圧特性が得られ、欠陥数は 0 となった。ウィークスポット酸化結晶化熱処理により、初期欠陥密度は 0.12 /cm² 以下に下がることが確認できた。ウィークスポットは、膜厚のばらつき、異物起因の局所的な薄膜化した部分については、界面酸化により絶縁性が回復する。また、結晶化により、膜質が飛躍的に均一化し、欠陥密度も減少する。結晶化により生成する結晶粒界、ピンホールが新たなウィークスポットになると考えられるが、同時に進む界面酸化により耐圧の低下に至らなかったと考えられる。結晶化による膜質

図 2-19 Ta<sub>2</sub>O<sub>5</sub> キャパシタの初期耐圧分布

の均一化は製品への適用において極めて重要な特性といえる。

従って、ウィークスポット酸化結晶化熱処理は  $Ta_2O_5$  膜の信頼性を大きく向上させることができ、製品適用に必須の工程である。

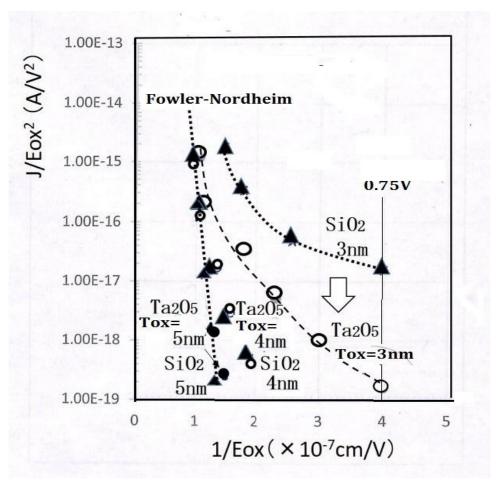

## 2.5.4 電気伝導特性

図 2-20 に、 $SiO_2$  換算膜厚で 3, 4, 5 nm の  $Ta_2O_5$  膜と熱酸化  $SiO_2$  膜との電流 一電圧特性の比較を示している。ここで、Eox は  $SiO_2$  膜に換算して求めた電界 強度であり、 $SiO_2$  単層膜からできていると仮定して計算したものである。プロットは Fowler-Nordheim 伝導式(2-1)式に従って、プロットした。

$$J = AE^{2}exp(-B/E)$$

(2-1)

A,B は定数であり、E は電界強度であり、ここでは Eox で置き換えられる。  $J/E_{OX}$  vs  $1/E_{OX}$  が直線にプロットできる場合には、Fowler-Nordheim 伝導と

図 2-20 SiO<sub>2</sub> 換算膜厚 3, 4, 5 nm の Ta<sub>2</sub>O<sub>5</sub> と SiO<sub>2</sub> 膜の伝導機の比較、Ta<sub>2</sub>O<sub>5</sub> 膜は○、SiO<sub>2</sub> 膜は▲

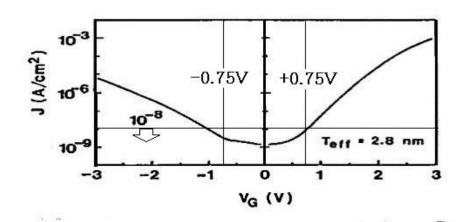

判断できる。 $SiO_2$  膜は高電界を印加する場合には Fowler-Nordheim 伝導に従う。図 2-20 に|示すように、 $SiO_2$  膜が 5 nm ではプロットは直線に従い、Fowler-Nordheim 伝導に従う。一方、 $SiO_2$  膜が 4 nm、3 nm と薄膜化すると、直接トンネリング電流が増加し、3 nm ではリーク電流が大幅に増加し、直線近似とならない。一方、 $SiO_2$  換算膜厚で 4,5 nm の  $Ta_2O_5$  膜では、 $SiO_2$  膜と同等な伝導特性を示すが、 $SiO_2$  換算膜厚で 3 nm に薄膜化した  $Ta_2O_5$  膜では、 $SiO_2$  膜に比較してリーク電流は約 2 桁小さくなることがわかった(印加電圧は DRAM 動作電圧 0.75 V)。

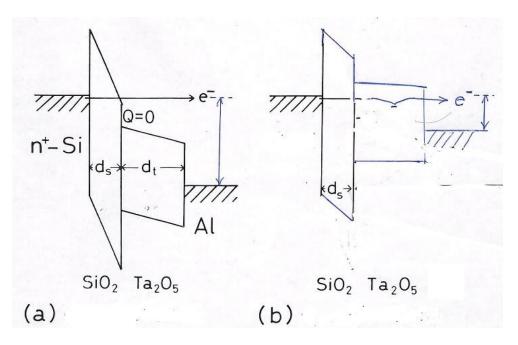

図 2-21 に  $Ta_2O_5/SiO_2$  積層膜のバンド構造模式図を示す。高電圧では Fowler-Nordheim 伝導に従うが、低電圧では  $Ta_2O_5/SiO_2$  積層膜の直接トンネリングとなると考えられる。 $SiO_2$  換算膜厚が 3 nm で比較すると、低電圧では  $Ta_2O_5/SiO_2$  積層膜のリーク電流が単層の  $SiO_2$  膜のリーク電流より少ない。この理由は、高誘電率膜を用いることで、相対的に膜厚が厚くなり、直接トンネル電流が抑制され

図 2-21 Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> 積層膜のバンド構造模式図 (a) 高電圧 (b) 低電圧

るためと考えられる。バイポーラメモリ素子の動作電圧は $0.5\,V$ であるので、低電圧の伝導機構では $Ta_2O_5/SiO_2$ 積層膜を介した直接トンネリングが主体となり、 $Ta_2O_5/SiO_2$  積層膜が $SiO_2$  単層膜よりリーク電流が少ない状態で動作させることとなる。また、 $64\,$  メガビット DRAM 以降の素子でも、動作電圧は $0.75\,$  V (電源電圧の半分:1/2Vcc) 以下となるので、同様に直接トンネリングを抑制できる領域で使用することになる。バイポーラメモリ素子では、DRAM と比較してリーク電流の制約は厳しくなく、 $SiO_2$  換算膜厚 $3\,$ nm においても、動作電圧 $0.5\,$  V における目標とする $0.01\,$   $A/cm^2\,$  以下のリーク電流は達成可能である。従って、 $2.1\,$  節で示したように、第二の課題である、電気的特性の安定性、欠陥密度、絶縁破壊信頼性などの製品レベルでの高信頼性がより重要な課題となった。

#### 2.5.5 界面安定性

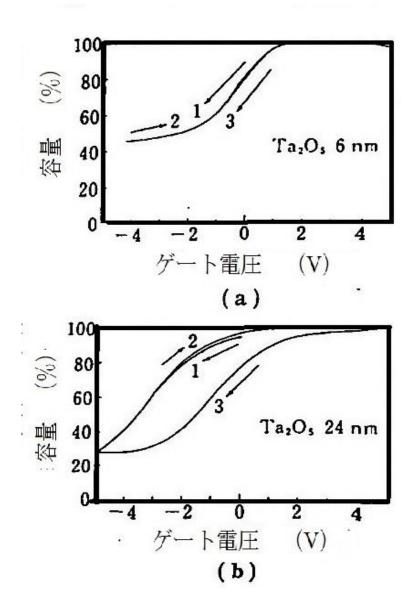

シリコン基板表面にスパッター法により  $Ta_2O_5/SiO_2$  膜を形成した場合には、界面に  $SiO_2$  が存在するために、 $Ta_2O_5/SiO_2$  の界面不安定性が懸念される。図 2-22 (a)、(b) にそれぞれ、膜形成後に高温熱処理しない 6 nm と 24 nm の  $Ta_2O_5$  キャパシタの容量一電圧 (C-V) 特性をそれぞれ示す。(b) の  $Ta_2O_5$  膜が厚い場合には、ゲート電圧を掃引するたびに C-V 特性の変動を生じる。一方、(a) のように、 $Ta_2O_5$  膜厚が薄くなるにつれ、界面の不安定性が解消ししていくことがわかる。

図 2.22 Ta2O5 キャパシタの C-V 特性のヒステリシス評価

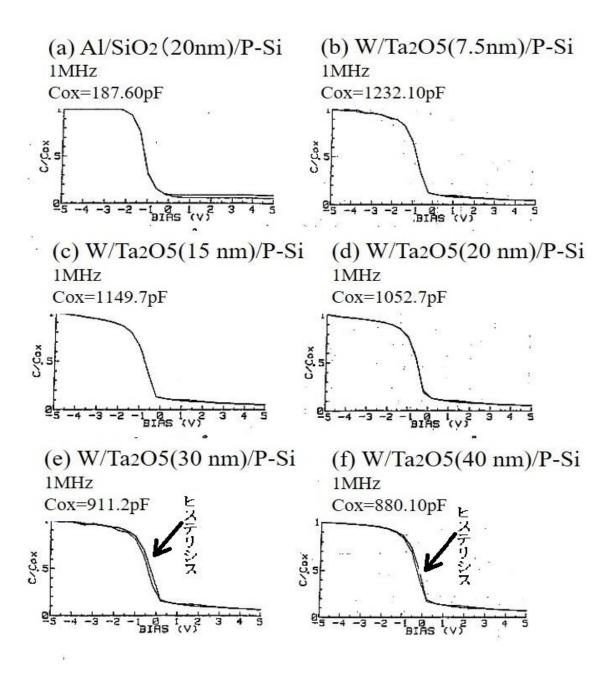

一方、図 2-23 は乾燥酸素囲気中で 800  $^{\circ}$ C、30 分の乾燥酸素熱処理を行った SiO<sub>2</sub> 単層膜と Ta<sub>2</sub>O<sub>5</sub> キャパシタの C-V 特性によるヒステリシスを観察したもの である。SiO<sub>2</sub> 単層膜の膜厚は 20 nm, Ta<sub>2</sub>O<sub>5</sub> 膜の膜厚は 7.5, 15, 20, 30, 40 nm について測定しているが、30、40 nm ではヒステリシスが観測できるが、20 nm 以下の薄膜ではヒステリシスは測定できなかった。 ウィークスポット酸化結晶 化熱処理(800  $^{\circ}$ C、30 分の乾燥酸素熱処理)による結晶化により、膜中の電荷のトラップは大幅に減少することを示唆している。

従って、膜厚が 20 nm 以下の反応性スパッター法による Ta<sub>2</sub>O<sub>5</sub> 膜にウィーク

スポット酸化結晶化熱処理 (800  $\mathbb{C}$ 、30 分の乾燥酸素熱処理) を行うことより、形成される  $Ta_2O_5/SiO_2$  積層膜の C-V 特性にヒステリシスは観察されず、安定していることがわかった。

図 2-23 乾燥酸素雰囲気での熱処理後の Ta<sub>2</sub>O<sub>5</sub> 膜の C-V 特性ヒステリシス評価

## 2.5.6 経時的絶縁破壊信頼性評価(TDDB 特性評価)

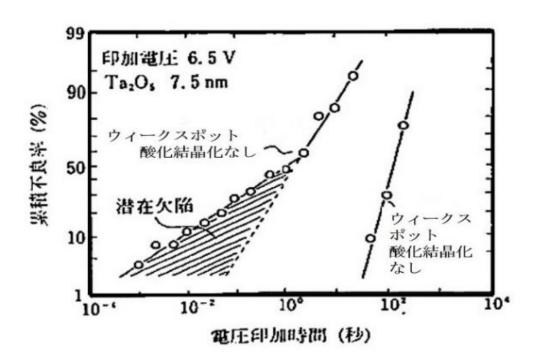

絶縁膜の欠陥としては、初期的欠陥以外に潜在的欠陥があると考えられる。潜在的欠陥は、初期的には欠陥ではないが、ストレス電圧の印加とともに、劣化が始まり絶縁耐圧の低下、もしくは、絶縁破壊に至る欠陥と定義できる。図 2-24はウィークスポット酸化結晶化前後の経時的絶縁破壊特性 (以下、TDDB 特性: Time Dependent Dielectric Breakdown) の比較を示している。 $Ta_2O_5$  膜厚 7.5 nm にストレス電圧  $6.5\,V$  を印加して、累積不良率の時間依存性を評価している。ウィークスポット酸化結晶化熱処理を行わない場合には、短いストレス時間の間に不良となる潜在欠陥が多くみられるが、ウィークスポット酸化結晶化熱処理により、潜在欠陥がなくなることがわかる。この結果は、ウィークスポット酸化結晶化工程により、潜在欠陥も修復されることを示している。

図 2-24 ウィークスポット酸化結晶化による TDDB 特性の向上

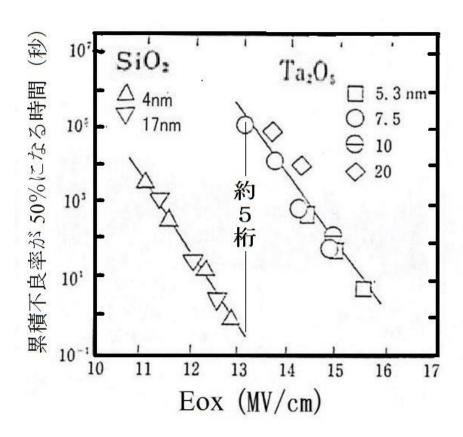

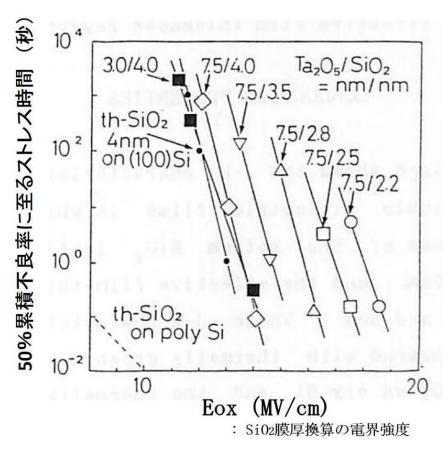

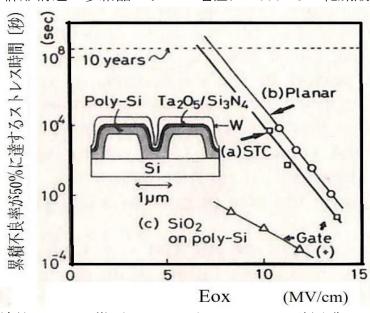

さらに、TDDB 特性の評価により、長期的絶縁破壊信頼性について、単結晶シリコン上の熱酸化  $SiO_2$  との比較が可能となる。図 2-25 は累積不良率が 50 %に至るストレス時間の  $SiO_2$  換算膜厚での電界強度  $E_{OX}$  のストレス依存性を示しいる。リーク電流が同等な  $SiO_2$  換算膜厚 4 nm の膜( $Ta_2O_5$  膜厚 10 nm)を適用する場合であっても、4 nm の単層の熱酸化  $SiO_2$  膜よりも同一のストレス電界強度において、約 5 桁も絶縁破壊寿命が長く、優れた長期信頼性を示す。

図 2-25 50%累積不良率に至る絶縁破壊時間のストレス電界強度依存性

以上のように、 $Ta_2O_5/SiO_2$  積層構造は、ウィークスポット酸化結晶化工程により、初期欠陥、潜在欠陥を低減できるうえに、長期的絶縁破壊信頼性において、熱酸化  $SiO_2$  膜よりも大幅に優れていることがわかった。 $Ta_2O_5/SiO_2$  積層膜をバイポーラメモリ素子に適用することで、製品の信頼性を飛躍的に高めることができる。また、DRAM 等への適用にあたっても、優れた長期信頼性を確保できることから、 $Ta_2O_5/SiO_2$  積層膜は極めて有望なメモリ用容量絶縁膜であることがわかった。

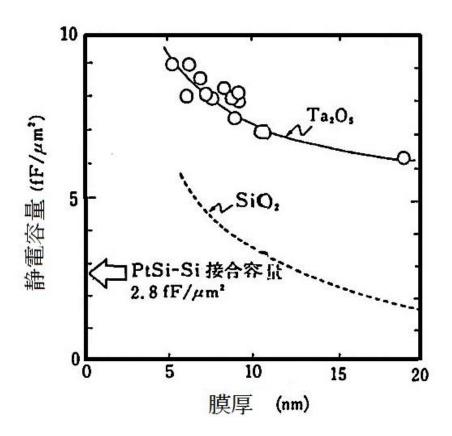

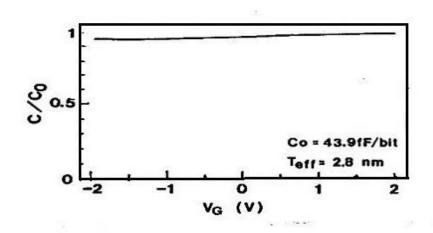

#### 2.5.7 静電容量

図 2-26 に 800  $\,^\circ$ C、30 分の乾燥酸素熱処理であるウィークスポット酸化結晶 化熱処理を行った  $Ta_2O_5$  キャパシタについて膜厚と容量の関係を示す。 $Ta_2O_5$  膜厚が 20 nm で容量は  $SiO_2$  の約 4 倍、10 nm 以下で約 2 倍の容量を有している。これは、 $Ta_2O_5$  の薄膜化に対して相対的に  $Ta_2O_5$  と Si の界面に誘電率の小さい  $SiO_2$  層が増加するためである。また、 $Ta_2O_5$  の薄膜化を 4 nm まで行うと、 $SiO_2$  換算膜厚で 3 nm まで薄膜化できることがわかった。従って、目標である 7.5  $fF/\mu m^2$  から最大 11  $fF/\mu m^2$  までの容量増加が可能となった。

図 2-26 Ta2O5 キャパシタ容量の膜厚依存性

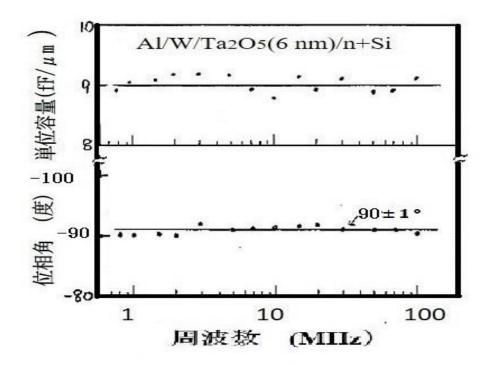

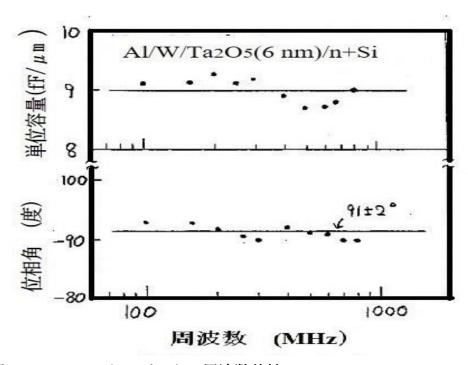

#### 2.5.8 高周波特性

$Ta_2O_5$  膜を高速バイポーラメモリ素子に適用する場合に、300 MHz 程度までは容量の低下がないことが望ましい。図 2-27、図 2-28 は膜厚 6 nm の  $Ta_2O_5$ キャパシタの静電容量、位相角の周波数依存性を示す。図 2-27 は 80 KHz から 100 MHz まで、図 2-28 は 100 MHz から 800 MHz までの容量範囲の実験結果をそれぞれ示している。800 KHz から 300 MHz までは容量は  $90\pm0.4~\mathrm{fF/\mu m^2}$  の範囲にある。従って、Si 半導体素子への適用において必要とされる、高周波特性を満足する。周波数が  $400~\mathrm{MHz}$  以上では測定点のバラツキが大きくなるが、これは主に、試料を納めるパーケージのインダクタンス L および直列抵抗 R による共振が起こり、その補正誤差によるものである。従って、容量の周波数変動がバイポーラメモリの動作に悪影響を与えることはない。

図 2-27 Ta<sub>2</sub>O<sub>5</sub> キャパシタの周波数特性 80 KHz-100 MHz

図 2-28 Ta<sub>2</sub>O<sub>5</sub> キャパシタの周波数特性 60 MHz-800 MHz

# 2.6 反応性スパッターTa<sub>2</sub>O<sub>5</sub>膜のバイポーラメモリ素子用容量絶縁膜への適用

Ta<sub>2</sub>O<sub>5</sub> キャパシタを用いた高速バイポーラメモリにより、16 キロビットバイポーラメモリ容量として必要な性能を達成することができた。主な要求仕様と得られた実績を示す。

- (1) 単位容量の目標: $7.5 \, \mathrm{fF}/\mu\mathrm{m}^2$ 以上

- $\rightarrow$  8.5 fF/ $\mu$ m<sup>2</sup>以上最大 11 fF/ $\mu$ m<sup>2</sup>(目標より 30%以上の容量増加)

- (2) 欠陥密度の目標: <1.0/cm<sup>2</sup>

- $\rightarrow$  ウィークスポット酸化結晶化熱処理により<1.0/cm<sup>2</sup>を達成。

- (3) 高周波特性の目標:300 MHz まで一定の容量

- → ウィークスポット酸化結晶化熱処理により 300 MHz まで一定。

- (4) リーク電流の目標:動作時 0.5 V で < 0.01 A/cm<sup>2</sup>

- $\rightarrow$  0.5 V で $<10^{-7}$  A/cm<sup>2</sup> 以下 (0.75 V で $<10^{-6}$  A/cm<sup>2</sup> 以下: 図 2-20)

- (5) 絶縁耐圧の目標:2 V以上

- → 4-5 V (1000 秒の絶縁破壊寿命): 図 2-25

図 2-29 は本開発により製造された、Ta<sub>2</sub>O<sub>5</sub> キャパシタを用いた 16 キロビット高

図 2-29 高速バイポーラメモリセルの縮小

速バイポーラメモリと従来の PtSi-SBD 容量を用いた 4 キロビットメモリセルの比較を示している。  $Ta_2O_5$  膜の膜厚は 7.5 nm(Tox=4 nm、8.5 fF/ $\mu$ m²)であり、メモリセル面積を 1/3 に縮小することができた。 開発時は 16 キロビット高速バイポーラメモリとしては世界最速のアクセス時間 4 ns を達成することができた。

## 2.7 まとめ

Si 半導体メモリに初めて高誘電率誘電体を適用することに成功した。この 最も大きな成功の要因はウィークスポット酸化結晶化工程にある。本研究以前 においては、 $Ta_2O_5$  膜は 600  $\mathbb{C}$ の熱処理により絶縁耐圧が低下し、700  $\mathbb{C}$ 以上の 熱処理により結晶化し、クラックが生成するものと考えられていた。しかしなが ら、10 nm 以下まで薄膜化する場合には、異なる現象が起きることがわかった。 つまり、ウィークスポット酸化結晶化工程により 10 nm 以下の Ta<sub>2</sub>O<sub>5</sub> 膜を熱処理 する場合には、Ta2O5 膜中を乾燥酸素が拡散律速により Si 基板表面に達するよ うになり、界面酸化が起きる。更に、局所的に乾燥酸素が拡散しやすい場所に選 択的に酸化が進むと考えられる。ウィークスポット酸化結晶化工程により、絶縁 膜中の欠陥が修復され、信頼性が大幅に改善されたことから、局所的な薄膜領域 や結晶化の際に生成する微小なピンホールなどのウィークスポットにおいて、 結晶化と同時に Si の界面酸化により選択的に酸化による欠陥修復がなされ、良 好な絶縁性が維持されたものと推定している。これをウィークスポット酸化結 晶化モデルと命名した。また、Ta2O5膜の結晶化はC-V特性の不安定性の原因と なるトラップをなくすとともに、結晶化により比誘電率を非晶質より30%増加 させるうえに、絶縁膜特性が飛躍的に均一化するなどの特性改善をもたらす。ま た、ウィークスポット酸化結晶化工程は欠陥密度を低減するだけでなく、経時的 絶縁破壊特性の改善をもたらした。Ta2O5/SiO2 積層膜の絶縁破壊寿命は、同じ SiO<sub>2</sub> 換算膜厚の単結晶シリコン上 SiO<sub>2</sub> 膜と比較して、約5桁長いことがわかっ た。これらの結果は、従来の容量絶縁膜を積極的に Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> 積層膜に置き換え ることにより、高い信頼性が得られることを示唆するものであった。

誘電体は非晶質であるべきと思っていたが、 $Ta_2O_5$  膜を結晶化することによって、極薄膜でありながら極めて信頼性の高い誘電体膜が得られたことは驚きである。結晶化と界面酸化の微妙な調和こそがこの技術の本質である。

# 2.8 参考文献

- [1] S. Asai, "Trend in megabit DRAMs," in IEDM Tech. Dig., p.368, 1984

- [2] J. Yugami, T. Mine. Iijima, and A. Hiraiwa, "Inter-poly SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> capacitor films 5 nm thick for deep submicron LSIs," in Extended abstract 20<sup>th</sup> Conf. on

- Solid State Devices and Materials, (Tokyo, 1989) p.173.

- [3] H. Shinriki, Y. Nishioka, Y. Ohji and K. Mukai, "Oxidized Ta2O5/Si3N4 Dielectric Films on Poly-Crystalline for dRAM's" IEEE Transactions on Electron Devices Vol.ED-36, No.2, February p.328, 1989

- [4] H. Shinriki, T. Kisu, S. Kimura, Y. Nishioka, Y. Kawamoto and K. Mukai, "Promising Storage Capacitor Structures with Thin Ta2O5 Film for Low-Power High-Density DRAM's" IEEE Transactions on Electron Devices Vol.ED-37, No.9, September p.1939, 1990.

- [5] Y. Nishioka, H. Shinriki and K. Mukai "Influence of SiO<sub>2</sub> at the Ta<sub>2</sub>O<sub>5</sub>/Si interface on dielectric characteristics of Ta<sub>2</sub>O<sub>5</sub> capacitors" J. Applied Physics Vol. 61, Number 6, pp.2335-2338, 1987.

- [6] Y. Nishioka, H. Shinriki and K. Mukai "Time Dependent Dielectric Breakdown Characteristics of Ta<sub>2</sub>O<sub>5</sub>/ SiO<sub>2</sub> Double Films" J. Electrochem. Soc. 136, No.3, pp.872-873, 1989.

- [7] 西岡 泰城、神力 博:応用物理 第58巻、第11号(1989) "高誘電率 絶縁膜 Ta<sub>2</sub>O<sub>5</sub>の VLSI への応用"

- [8] Y. Nishioka, S. Kimura, H. Shinriki and K. Mukai "Dielectric Characteristics of Double Layer Structure of Extremely Thin Ta<sub>2</sub>O<sub>5</sub>/ SiO<sub>2</sub> on Si" J. Electrochem. Soc. 134, pp.410-415, 1987.

- [9] Y. Nishioka, N. Honmma, H. Shinriki, K. Mukai, K. Yamaguchi, A. Uchida, K. Higeta and K. Ogiue "Ultra-Thin Ta<sub>2</sub>O<sub>5</sub> Dielectric Film for High-Speed Bipolar Memories" IEEE Transactions on Electron Devices Vol.34, No.9, September p.1957, 1987.

- [10] H. Shinriki and M. Nakata, "UV-O<sub>3</sub> and Dry-O<sub>2</sub>: Two-Step Annealed Chemical Vapor-Deposited Ta<sub>2</sub>O<sub>5</sub> Films for Storage Dielectrics of 64-Mb DRAM's" IEEE Transactions on Electron Devices Vol.ED-38, No.3, March p.455, 1991.

- [11] J. Harvey and H. Wilman "The Crystallization of Thin Amorphous Tantalum Oxide Films Heated in Air or Vacuo, and the structure of the Crystalline Oxide" Acta

# 第3章 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub> 膜を有するキャパシタの基礎検討 3.1 緒言

第 2 章では、世界に先駆けてシリコン半導体素子製品に高誘電率誘電体を適用できたことを報告した。高誘電率膜としては  $Ta_2O_5$  膜を選択し、高誘電率  $Ta_2O_5$  膜を用いた容量を搭載することで、16 キロビットバイポーラメモリ素子の集積度を 4 倍としながら、メモリセル面積を 3 分の 1 に縮小することが可能となった。 Si 半導体素子に使われている単結晶シリコン上の熱酸化  $SiO_2$  膜を高誘電率  $Ta_2O_5$  膜に置き換える利点は、リーク電流の低減に加えて、信頼性の大幅な向上にあることを第 2 章にて報告した。この高信頼性が実現できたのは、反応性スパッター法により Si 基板上に形成した 10 nm 以下の  $Ta_2O_5$  膜を、800  $^{\circ}$   $^{\circ}$

バイポーラメモリ素子の容量は単結晶シリコン上に形成されているが、DRAM 素子の容量電極としては多結晶シリコン膜が使用され、容量絶縁膜も多結晶シリコン膜上に形成する必要がある。Ta<sub>2</sub>O<sub>5</sub> 膜を 64 メガビット DRAM 用積層容量型メモリセル(STC CELL: Stacked Capacitor Cell)の容量絶縁膜として検討する場合、以下の課題があると考えられる。

- (1) 多結晶シリコン電極上における  $SiO_2$  換算膜厚 3 nm 相当の低欠陥、高信頼の  $Ta_2O_5$  膜を有するキャパシタの形成

- (2) 積層容量型メモリセル (STC CELL) などの立体化された容量部を有する  $DRAM \sim OTa_2O_5$  膜を有するキャパシタの適用

- (3)  $Ta_2O_5$  膜を有するキャパシタの 16 メガビット DRAM プロセスで使用される高温プロセスへの適合性。

本章では、まず(1)に掲げた課題を、明らかとすることを目的とし、(2)、(3)の課題については、4章にて報告する。

一般に多結晶シリコンの熱酸化膜は、酸化時に形成される多結晶シリコン 表面の微細な凹凸のために単結晶 Si 基板上の熱酸化膜と比較してリーク電流が 大きく、このため長期信頼性も劣るという問題があった [1]。Ta<sub>2</sub>O<sub>5</sub>キャパシタ の形成に際しても、多結晶シリコン電極の影響が懸念される。特に、2章に報告したように、ウィークスポット酸化結晶化工程により Si 基板上の  $Ta_2O_5$  キャパシタの欠陥密度の低減、絶縁破壊信頼性の向上は界面  $SiO_2$  層の生成によるところが大きいと考えられる。ウィークスポット酸化結晶化工程により多結晶シリコン電極上でも Si 基板上と同様に優れた界面  $SiO_2$  層を形成でき、信頼性の改善ができるか懸念された。

3.2 節では、多結晶シリコン電極上に形成した  $Ta_2O_5$  膜の電気的特性、信頼性について評価した結果を報告する [2]。また、16 メガビット DRAM では多結晶シリコン電極上の容量絶縁膜として  $SiO_2/Si_3N_4$  積層膜が容量絶縁膜として提案された [3]。そこで、3.3 節では、比誘電率が  $22\sim28$  の  $Ta_2O_5$  膜と  $Ta_2O_5/Si$  界面に  $Si_3N_4$  膜を形成し、ウィークスポット酸化結晶化工程を  $Si_3N_4$  膜上に形成した  $Ta_2O_5$  膜にも適用することを検討した。 $Si_3N_4$  膜は多結晶シリコンよりも酸化されにくいので、ウィークスポット酸化結晶化熱処理により容量の減少を抑制することも期待できる [4]。

## 3.2 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub> キャパシタの検討 [2]

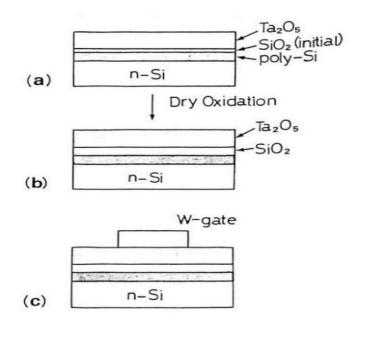

## 3.2.1 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub> キャパシタの形成方法 [2.5.6]

図 3-1 に示す工程により試料を作成した。Si 基板上に減圧 CVD 法により多結晶シリコン膜を 300 nm 形成し、875  $^{\circ}$ C、30 分のリン拡散を行った。その後、

図 3-1 Ta<sub>2</sub>O<sub>5</sub> キャパシタ製造方法

Ta<sub>2</sub>O<sub>5</sub> 膜形成前の洗浄として、AP 洗浄(アンモニア:過酸化水素=

2:1、温度 90 ℃、10 分)、及び、弗酸水溶液(弗酸:水=1:99、常温、10 秒) により、多結晶シリコン表面を水切れするまでエッチングを行った。次に、高誘 電率絶縁膜 Ta<sub>2</sub>O<sub>5</sub> を ULVAC 社のスパッター装置(ME58-0144)により、アルゴ ンと酸素の混合雰囲気中で高周波による反応性スパッター法で形成した。この 装置はロードロック(準備室)とスパッター室とに分かれており、スパッター室 は常時クライオポンプにより高真空( $10^{-9}$  Pa)に保たれている。 $Ta_2O_5$  膜形成の 為、ターゲットは純度 99.99 %の Ta ターゲットを使用し、10%の酸素入りアル ゴンガス 0.67 Pa、RF パワー300 W の条件においてスパッターを行った。 $Ta_2O_5$ 膜形成速度は、約1 nm/分である。ここで、Ta<sub>2</sub>O<sub>5</sub>膜の膜厚測定は、エリプソメト リーを用い、Ta<sub>2</sub>O<sub>5</sub> 膜の屈折率を 2.0 と仮定し、膜厚を求めた。エリプソメトリ ーによる Ta<sub>2</sub>O<sub>5</sub> 膜厚の誤差は、断面 TEM 写真から判定して± 10 %の範囲内であ ることを確認した。Ta<sub>2</sub>O<sub>5</sub>膜の形成初期では、多結晶シリコン表面がAr/O<sub>2</sub>プラ ズマに曝されて、極薄の $SiO_2$ 膜が生成される[5]。その後、 $Ta_2O_5$ 膜を連続して 堆積する。Ta<sub>2</sub>O<sub>5</sub> 膜形成後に乾燥酸素熱処理を行った。熱処理温度は 800、850、 900、950、1000 ℃で実施した。2 章では800 ℃、30 分の乾燥酸素熱処理をウィ ークスポット酸化結晶化熱処理として報告した。800℃以上の乾燥酸素熱処理は、  $Ta_2O_5$  膜を結晶化させるだけでなく、 $Ta_2O_5$  膜と多結晶シリコンの界面に  $SiO_2$  膜 を成長させる。熱処理後に上部電極としてタングステン電極を形成した。

#### 3.2.2 Ta<sub>2</sub>O<sub>5</sub> 膜と多結晶シリコン界面の SiO<sub>2</sub> 膜の成長

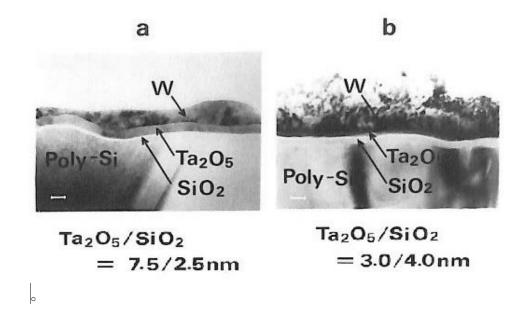

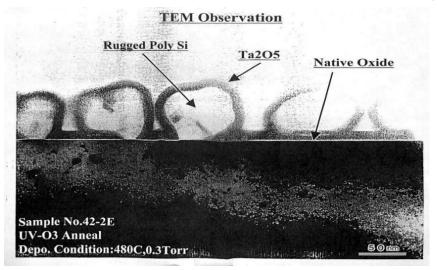

図 3-2 (a), (b)に示す様に、 $Ta_2O_5$  (7.5 nm)/ $SiO_2$  積層構造と  $Ta_2O_5$  (3.0 nm)/ $SiO_2$  積層構造の断面を透過電子顕微鏡( 断面 TEM )により測定した断面写真を示している。これらの試料は  $Ta_2O_5$  膜形成後に 850  $^{\circ}$  の乾燥酸化性雰囲気での熱処理を行った。界面の  $SiO_2$  の膜厚は  $Ta_2O_5$  膜が 7.5 nm の下層には 2.5 nm であり、 $Ta_2O_5$  膜が 3 nm の下層には 4.0 nm 形成されていることがわかる。界面に形成される  $SiO_2$  膜の膜厚は単結晶シリコン基板上と同様に多結晶シリコン上においても、 $Ta_2O_5$  膜厚に依存している [6]。

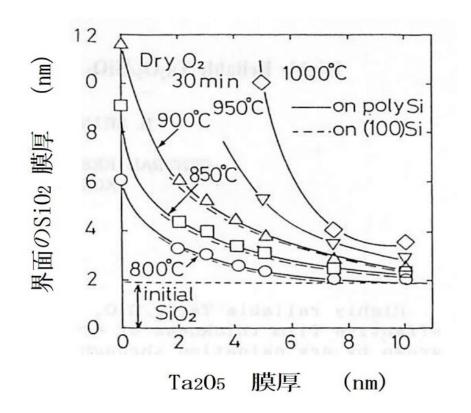

図 3-3 は乾燥酸素雰囲気の熱処理温度をパラメータとして、多結晶シリコン上と単結晶シリコン上について界面  $SiO_2$  膜厚の  $Ta_2O_5$  膜厚依存性を示している。 界面  $SiO_2$  膜厚は熱処理前後での容量の変化から成長した界面  $SiO_2$  膜厚を求めた。 界面  $SiO_2$  膜の成長は  $Ta_2O_5$  膜厚が厚いほど抑制され、単結晶シリコン上でも多結晶シリコン上でも界面の  $SiO_2$  膜の成長はほぼ同じであったことから、酸化種である酸素分子の  $Ta_2O_5$  膜中の拡散が律速となる酸化と考えられる [2,7]。

図 3-2 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> 積層膜の断面 TEM 写真

図 3-3 多結晶シリコン/Ta<sub>2</sub>O<sub>5</sub> 膜界面の乾燥酸素熱処理による酸化層形成

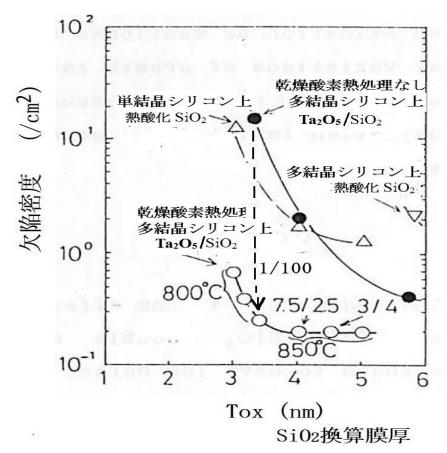

図 3-4 は多結晶シリコン上の  $Ta_2O_5/SiO_2$  積層膜を用いたキャパシタの欠陥 密度と多結晶シリコン、単結晶シリコン上の熱酸化による  $SiO_2$  キャパシタの欠陥密度を比較したものである。本章では、多結晶シリコン上  $Ta_2O_5/SiO_2$  積層膜

図 3-4 多結晶シリコン上の Ta<sub>2</sub>O<sub>5</sub> キャパシタの欠陥密度

を用いたキャパシタを  $Ta_2O_5/SiO_2$  キャパシタと記載する。多結晶シリコン上  $Ta_2O_5/SiO_2$  キャパシタの欠陥密度は乾燥酸素熱処理により、大幅に低減することがわかる。 $SiO_2$  換算膜厚で 3 nm において、単結晶シリコン上の熱酸化による $SiO_2$  膜の欠陥密度と  $Ta_2O_5$  膜成膜後に熱処理を行わない多結晶シリコン上  $Ta_2O_5/SiO_2$  膜の欠陥密度はほぼ同等であるが、800  $^{\circ}$  Cの乾燥酸素熱処理により、欠陥密度が約 100 分 1 に減少する。一方、多結晶シリコン上の熱酸化による  $SiO_2$  膜は 6 nm と厚くすることで、単結晶シリコン上の4 nm の熱酸化による  $SiO_2$  膜の欠陥密度と同等となるものの、更に薄膜化すると急激に欠陥密度が増加する。

従って、DRAM 積層型容量部の形成において、 $Ta_2O_5/SiO_2$  積層構造は多結晶シリコン蓄積電極上でも、欠陥密度の低い容量絶縁膜を形成できることを示している。第 2 章でウィークスポット酸化結晶化モデルに示したしたように、乾燥酸素雰囲気での熱処理により多結晶シリコン上  $Ta_2O_5/SiO_2$  キャパシタの欠陥密度が低減し、 $Ta_2O_5$  膜の結晶化とともに生成するピンホール等も、界面の $SiO_2$  膜の成長により修復されるものと考えられる。

#### **3.2.3** 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> キャパシタの **TDDB** 特性評価

図 3-5 は多結晶シリコン上  $Ta_2O_5/SiO_2$  キャパシタの経時的絶縁破壊特性 (TDDB 特性: Time Dependent Dielectric Breakdown) であり、累積不良率が 50% に至る寿命の  $SiO_2$  換算膜厚での電界強度 Eox 依存性を示している。ここでは、 $Ta_2O_5$  膜厚を 7.5 nm と一定として、界面の  $SiO_2$  膜厚をパラメータとして評価している。比較として、単結晶シリコン上の 4 nm の  $SiO_2$  膜、及び、多結晶シリコン上の 6 nm の熱酸化による  $SiO_2$  膜を容量絶縁膜とするキャパシタの TDDB 特性と比較している。多結晶シリコン上の熱酸化による  $SiO_2$  膜は 10 MV/cm 以下のストレス電界強度でも、短時間で絶縁破壊する。一方、多結晶シリコン上  $Ta_2O_5/SiO_2$  キャパシタの TDDB 特性は、単結晶シリコン上の熱酸化膜の TDDB 特性よりすぐれた特性を得ることができた。2.3 節に示した様に、反応性スパッターによる  $Ta_2O_5$  膜の成膜の際には、1.8-1.9 nm の界面の  $SiO_2$  膜が成長し、乾燥酸素熱処理により、更に増膜する。この過程により形成される多結晶シリコン上の  $Ta_2O_5/SiO_2$  積層膜により、優れた長期的信頼性を有する容量絶縁膜を実現することができた。界面の  $SiO_2$  膜の膜厚を 2.8 nm として、 $Ta_2O_5$  膜厚を 2.5 nm

図 3-5 多結晶シリコン上 Ta2O5/SiO2 キャパシタの TDDB 特性

とし、 $SiO_2$  換算膜厚で 4 nm に相当する多結晶シリコン上  $Ta_2O_5/SiO_2$  キャパシタの絶縁破壊寿命は、同一ストレス電界 Eox ( 例えば 14 MV/cm ) における単結晶シリコン上の 4 nm の熱酸化による  $SiO_2$  膜を用いたキャパシタの絶縁破壊寿命に比較して、約 5 桁以上長いことが推定できる。これは、図 2-25 に示す単結晶シリコン電極上の  $Ta_2O_5/SiO_2$  キャパシタの TDDB 特性と遜色ない。多結晶シリコン上の容量絶縁膜として  $SiO_2$  換算膜厚 Tox が 4 nm の容量絶縁膜として、 $Ta_2O_5/SiO_2$  積層膜が初めて、実用レベルの絶縁破壊信頼性を達成できたことは、当初の懸念を打ち消すものであり、ウィークスポット酸化結晶化処理の効果が多結晶シリコン上でも有効であることを示すものであった。

界面の SiO<sub>2</sub> 膜の膜厚が薄膜化する程、同一のストレス電界強度 Eox での絶 縁破壊寿命は増加し、界面の SiO2 膜厚が 4 nm では、単結晶シリコン上の 4 nm の熱酸化による SiO<sub>2</sub> 膜と同等の TDDB 特性を示す。また、Ta<sub>2</sub>O<sub>5</sub> 膜厚を 3 nm と しても、界面の SiO<sub>2</sub> 膜が 4 nm では、同等の TDDB 特性を示した。従って、 Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> 積層膜の絶縁破壊寿命の Eox 依存性は界面の SiO<sub>2</sub> 膜の絶縁破壊特性 に依存していると推測できる。熱酸化による SiO2 膜の単層膜の TDDB 特性の膜 厚依存性によれば、5 nm 以下の膜厚領域において、SiO2 膜厚が薄膜化するほど、 一定のストレス電界強度による絶縁破壊寿命は急激に長くなることが報告され ている [8]。直接トンネリング電流が増加することにより、SiO2 膜がダメージを 受けにくくなるためと考えられる。絶縁破壊寿命が界面の SiO<sub>2</sub> 膜厚に依存する ことから、Ta<sub>2</sub>O<sub>5</sub> 膜は絶縁破壊しにくい材料であり、SiO<sub>2</sub> 膜が最初に絶縁破壊し たと同時に、すべてのストレス電圧が Ta2O5 膜に印加されて、積層膜の絶縁破壊 に至ると解釈できる。図 2-35 の TDDB 特性は、Ta<sub>2</sub>O<sub>5</sub> 膜厚によらず、界面 SiO<sub>2</sub> 膜厚が一定なために、ほぼ同等の TDDB 特性が得られている。従って、 $Ta_2O_5/SiO_2$ 積層膜の絶縁破壊寿命は、界面の SiO2 膜を薄膜化するほど、同一電界強度 Eox に対して、より絶縁破壊しにくくなる。界面酸化膜の膜厚を  $2.2\,\mathrm{nm}$  として、 $\mathrm{Ta_2O_5}$ 膜厚を 7.5 nm とし、SiO2 換算膜厚で 3.5 nm に相当する多結晶シリコン上に形成 した Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> キャパシタの絶縁破壊寿命は、更に、長くなる。64 メガビット DRAM に必要とされる  $SiO_2$  換算膜厚 Tox が 3 nm の容量絶縁膜の構成としては、 Ta<sub>2</sub>O<sub>5</sub> 膜厚 4-5 nm であり、界面の SiO<sub>2</sub> 膜が 2.2 nm 以下に制御されることが想定 できる。この Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> 積層膜の構成としては、界面 SiO<sub>2</sub> 膜をより薄膜化して、 絶縁破壊信頼性を向上することが望ましい。

以上の検討から、64 メガビット DRAM 以降の積層型 DRAM の高集積化を 進めるためには、多結晶シリコン電極表面上に形成した  $Ta_2O_5/SiO_2$  積層膜を容 量絶縁膜とするのが有力な選択肢であることがわかった。

#### 3.2.4 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> キャパシタの電流 - 電圧特性

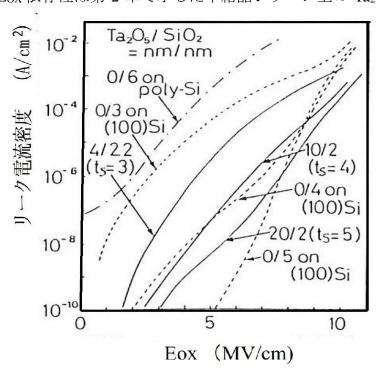

多結晶シリコン上の  $Ta_2O_5/SiO_2$  積層膜のリーク電流の  $SiO_2$  換算膜厚での電界強度 Eox 依存性は第 2 章で示した単結晶シリコン上の  $Ta_2O_5/SiO_2$  積層膜のリ

図 3-6 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> キャパシタの電流―電圧特性

ーク電流のSiO<sub>2</sub>換算膜厚での電界強度Eoxの依存性と遜色ないことがわかった。 従来、多結晶シリコンを熱酸化する場合には、形成された熱酸化膜の膜厚は、多 結晶表面の結晶方位による酸化速度の違いにより変動し、酸化中に表面に凹凸 が生成することなどにより、初期欠陥密度の増加、リーク電流の増加、絶縁破壊 信頼性の低下の原因となる。図 3-6 に示すように、多結晶シリコン上の 6 nm の SiO<sub>2</sub> 膜のリーク電流は単結晶シリコン上と比較して 5 桁以上のリーク電流の増 加が認められ、容量絶縁膜としての適用することはできない。しかしながら、多 結晶シリコン上の Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> 積層膜については、研究着手時の多結晶シリコン 上の界面 SiO<sub>2</sub> 膜の信頼性への懸念に反し、多結晶シリコン上でも単結晶シリコ ン上における Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> 積層膜の電流一電圧特性と遜色ない容量絶縁膜が形成 できたことは驚きであった。これは、ウィークスポット酸化結晶化工程において、 乾燥酸素の Ta<sub>2</sub>O<sub>5</sub> 膜中の拡散が遅いために、Ta<sub>2</sub>O<sub>5</sub> 膜の結晶化により生成する微 細なピンホールや結晶粒界の下層の多結晶シリコン界面が選択的に酸化され、 局所的な絶縁耐圧の低下が防止できたことによると考える。また、乾燥酸素の供 給が Ta<sub>2</sub>O<sub>5</sub> 膜中の拡散律速となることにより、多結晶シリコン上の結晶面の違い による酸化膜厚の違いが抑制され、多結晶シリコン上の酸化膜においても高い 信頼性が確保できたと推定している。

# 3.3 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub> キャパシタの検討 [4]

多結晶シリコン上の  $Ta_2O_5$  界面に形成される  $SiO_2$  膜の影響を除き、より良好な容量膜を形成する目的で、多結晶シリコン表面に  $Si_3N_4$  膜を形成した後、  $Ta_2O_5$  膜を形成し、ウィークスポット酸化結晶化熱処理をすることを検討した。

## 3.3.1 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub> キャパシタの形成方法

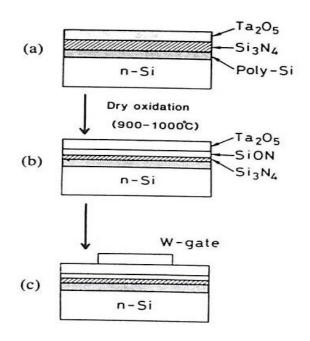

図 3-7 は  $Ta_2O_5/Si_3N_4$  積層膜を有するキャパシタの形成方法を示している。 単結晶シリコン基板上に多結晶シリコンを形成した後、高濃度のリンをドープした。多結晶シリコン表面を弗酸により洗浄した後、減圧 CVD 法によって  $Si_3N_4$  膜 (6 nm)を形成した。99.99 %純度の Ta ターゲットを用いて、 $Ta_2O_5$  膜 (7.5 nm)を反応性スパッターにより  $Si_3N_4$  膜上に形成した。Ta ターゲットの純度は 99.99 %であった [3,4]。その後、900、950、1000  $^{\circ}$  において、乾燥酸素雰囲気において、30 分の熱処理を行った。 $Ta_2O_5/Si_3N_4$  界面において、 $Si_3N_4$  膜が酸化される。界面に酸窒化膜が形成されるのか、酸化膜が形成するのは明確ではない。 その後、上部電極としてタングステンをスパッター法により、200 nm 形成した。

Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub> 積層膜と比較するために、Ta<sub>2</sub>O<sub>5</sub> (28 nm) / SiO<sub>2</sub> (1.5 nm) 積層構

図 3-7 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub> キャパシタの製造方法

造のキャパシタを形成した。 $Ta_2O_5$  膜を形成した後、乾燥酸素雰囲気において、900  $\mathbb{C}$ 、30 分の熱処理をおこなった。タングステンを上部電極としてスパッター法により形成した。また、多結晶シリコン上に、1000  $\mathbb{C}$  の乾燥酸化性雰囲気での熱酸化により 10 nm の酸化シリコン膜を形成した。 $SiO_2$  膜上にリンドープの多結晶シリコン膜を上部電極として形成した。それぞれの膜厚はエリプソメトリーにより評価し、断面 TEM 写真により補正することで、算出した。

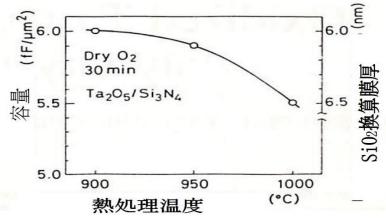

#### 3.3.2 多結晶シリコン上 Ta2O5/Si3N4 キャパシタの熱処理温度依存性

図 3-8 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub> キャパシタの乾燥酸素熱処理 による容量変化

乾燥酸化性雰囲気での熱処理温度画 900  $\mathbb{C}$ から 1000  $\mathbb{C}$ に成長するとともに、 $Ta_2O_5/Si_3N_4$  キャパシタの容量は 6.0  $fF/\mu m^2$  から 5.5  $fF/\mu m^2$  に減少する。従って、熱処理により  $Si_3N_4$  膜の酸化が進んだと判断できる。対応する  $SiO_2$  換算膜厚は 6 nm から 6.5 nm に変化したことに相当する。

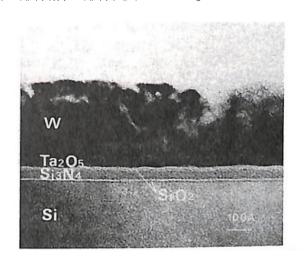

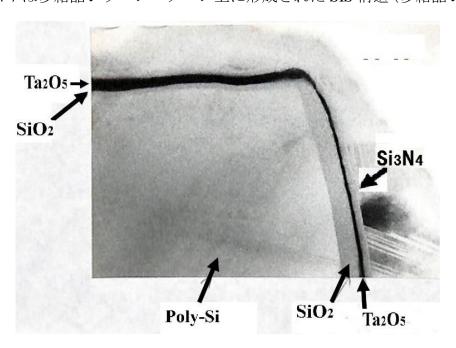

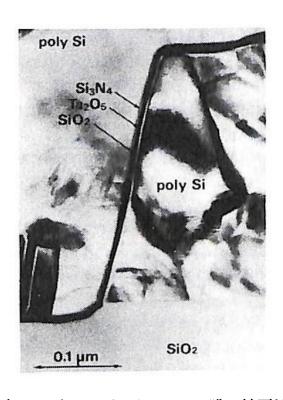

図 3-9 に示す断面 TEM 観察は単結晶シリコン上に形成した、1000  $^{\circ}$ C、30 分間の乾燥酸化性雰囲気で熱処理を行った  $Ta_2O_5(7.5 \, \text{nm})/Si_3N_4(6 \, \text{nm})$  の断面 TEM 写真である。 $Ta_2O_5$  膜、界面の  $SiO_2$ 、 $Si_3N_4$  膜、自然酸化膜、シリコン基板のそれぞれの境界が断面 TEM 写真に示されており、混合層の形成は 1000  $^{\circ}$ Cの 熱処理によっても、観察されなかった。界面  $SiO_2$  膜は熱処理後に形成され、自然酸化膜は  $Si_3N_4$  膜の形成前に形成されていた。

図 3-9 Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub>積層構造の断面 TEM 写真

#### 3-3-3 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub> キャパシタの電流-電圧特性

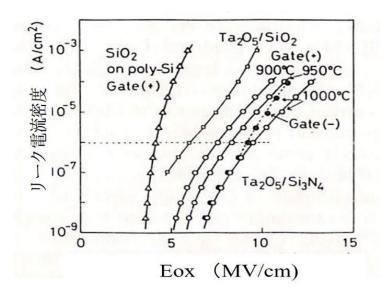

図 3-10 は、熱処理温度をパラメータとして、形成した  $Ta_2O_5/Si_3N_4$  積層膜を用いたキャパシタのリーク電流密度の  $SiO_2$  換算膜厚での電界強度  $E_{Ox}$  依存性を示している。熱処理温度が高いほど、リーク電流密度が減少する。 $Ta_2O_5$  (28 nm) / $SiO_2$  (1.5 nm) 積層構造のキャパシタのリーク電流密度は  $Ta_2O_5/Si_3N_4$  積層膜よりも大きいが、 $Ta_2O_5$  (28 nm) / $SiO_2$  (1.5 nm) 積層構造のキャパシタの容量が 7.2 fF/ $\mu$ m² と 10-20 %大きいことを考慮する必要がある。 $SiO_2$  換算膜厚 6-6.5 nm の領域では、 $Ta_2O_5/Si_3N_4$  積層膜は十分に低いリーク電流密度が得られるものの、 $SiO_2$  換算膜厚で 3-4 nm となる領域においてもで同じリーク電流密度の電界強度  $E_{Ox}$  依存性を示すかどうかは不明である。CVD 法による  $Si_3N_4$  膜を制御性よく薄膜化できるかも課題である。

図 3-10 多結晶シリコン上の Ta2O5/Si3N4 キャパシタの電流-電圧特性特性

#### 3.3.4 多結晶シリコン上 Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub> キャパシタの TDDB 特性

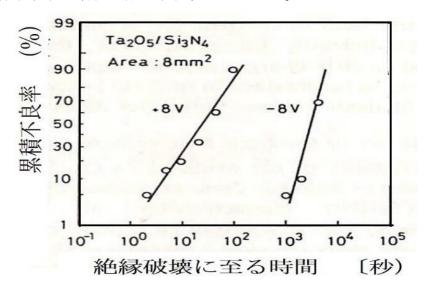

$Ta_2O_5/Si_3N_4$  キャパシタの信頼性を TDDB により評価した。図 3-11 は  $Ta_2O_5/Si_3N_4$  キャパシタに+8 V ストレス電圧印加と-8 V ストレス電圧印加により測定した TDDB 特性を示している。 $Ta_2O_5/Si_3N_4$  積層膜は 1000 °C、30 分の乾燥酸素熱処理を行った。キャパシタ面積は 8 mm²、それぞれ 30 ヶのキャパシタを測定した。累積不良率のストレス時間依存性は直線近似でき、直線を外れて短時間で絶縁破壊する潜在欠陥は顕在化していない。

図 3-11 多結晶シリコン電極上 Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub> キャパシタの累積不良率の ストレス時間依存性

図 3-12 多結晶シリコン上の Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub> 積層膜の TDDB 特性

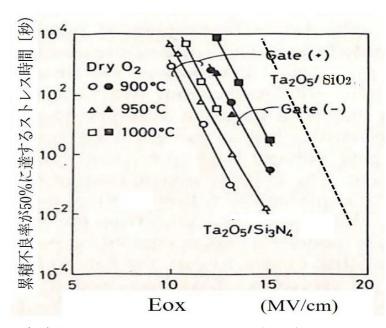

一方、図 3-12 は 50 %累積不良率のストレス時間依存性を示している。  $Ta_2O_5/Si_3N_4$  積層膜では、乾燥酸素熱処理温度が高いほど、TDDB 特性が改善されることを示しているが、高温の熱処理を行うと容量が低下してしまう。しかも、図 3-5 に示す  $Ta_2O_5/SiO_2$  積層膜の TDDB 特性を点線で示しているが、 $Ta_2O_5/Si_3N_4$  積層膜に比較すると、絶縁破壊寿命は約 4 桁以上絶縁破壊寿命が長いことがわかる。 $Si_3N_4$  膜を導入することにより、絶縁破壊の対する長期的信頼性は低下することは、 $Si_3N_4$  膜との積層化の課題といえる。

図 3-13 は櫛形構造の多結晶シリコン電極に 1000 ℃の乾燥酸素熱処理を行

図 3-13 多結晶シリコン櫛形パターン上 Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub> 積層膜の TDDB 特

った  $Ta_2O_5/Si_3N_4$  キャパシタの TDDB 特性を示している。櫛形構造は幅、深さが  $0.3\,\mu$ m、 $0.8\,\mu$ m であった。絶縁破壊寿命は平面型キャパシタ構造よりも一桁短く なることがわかった。従って、反応性スパッターによる  $Ta_2O_5$  膜によっても、アスペクト比が 3 以下のパターンであれば、積層型容量部に試験的に導入することは可能であることがわかった。4 章では、DRAM プロセスに反応性スパッター法による  $Ta_2O_5$  膜を導入して DRAM プロセスへの  $Ta_2O_5$  膜導入の影響について検討した結果を示す。

以上のように、 $Ta_2O_5/Si_3N_4$ キャパシタにより、 $SiO_2$ 換算膜厚 6-6.5 nm の領域において、良好なリーク電流、低欠陥、長期的絶縁破壊信頼性を得ることができた。ただし、以下の課題が挙げられる。

- ① 64 メガビット DRAM 用容量絶縁膜としては、SiO<sub>2</sub> 換算膜厚 3 nm の薄膜化が必要であり、CVD 法による Si<sub>3</sub>N<sub>4</sub> の薄膜化が課題となる。

- ② TDDB 特性は乾燥酸素熱処理温度が高い程改善されるが、容量は逆に 減少するトレードオフの関係にあり、高容量化(Tox の薄膜化)と高信頼 化がトレードオフの関係となってしまい、両立が難しい。

- ③ 多結晶シリコン上の  $Ta_2O_5/Si_3N_4$  キャパシタは  $Ta_2O_5/SiO_2$  キャパシタの TDDB 特性に比較して、絶縁破壊寿命は 4 桁以上低く、 $Si_3N_4$  膜を導入することで、絶縁破壊信頼性を低下させる。

#### 3.4 まとめ

多結晶シリコン電極上の $Ta_2O_5$ 膜を用いたDRAM用容量について検討した。 64 メガビットDRAM 以降に必要とされる $SiO_2$  換算膜厚 3 nm の容量絶縁膜として、多結晶シリコン上においても、動作電圧において目標のリーク電流以下を達成しながら、 $SiO_2$  換算膜厚 3 nm までの薄膜化が可能な $Ta_2O_5/SiO_2$  積層膜の検討を進めることが望ましい。 $Ta_2O_5/Si_3N_4$  積層膜構造により得られた $SiO_2$  換算膜厚は 6 nm であり、 $SiO_2$  換算膜厚 3 nm までの薄膜化には、 $Si_3N_4$  の薄膜化に課題がある。また、 $Ta_2O_5/SiO_2$  積層膜のTDDB 特性は $Ta_2O_5/Si_3N_4$  積層膜のTDDB 特性より優れていることがわかった。これは、積層膜の絶縁破壊を決定づけると思われる界面層を $Si_3N_4$  膜とするよりも $SiO_2$  膜とすることにより、より高い信頼性が得られることを示している。

多結晶シリコン上の熱酸化膜はリーク電流が増大し、信頼性が低下すると考えられていたが、高誘電体  $Ta_2O_5$  膜とシリコン界面に成長する  $SiO_2$  膜は、下地が多結晶シリコン電極であっても、ウィークスポット酸化結晶化処理により、欠陥が修復され、また、 $Ta_2O_5$  膜中の拡散律速による酸化により、多結晶シリコ

ン表面の結晶面依存性が緩和され、界面に良好な  $SiO_2$  膜を生成できたものと考えられる。4 章以降では、 $Ta_2O_5/SiO_2$  積層膜を 64 メガビット DRAM 用の容量絶縁膜として選定して、実用化を進めた結果について報告する。

## 3.5 参考文献

- [1] P A Heimann, S P Muraruka, and T T Sheng, "Electrical conduction and breakdown in oxides of polycrystalline silicon and their correlation with interface texture," J. Appl. Phys. 53, pp.6240-6245, 1982.

- [2] H. Shinriki, Y. Nishioka and K. Mukai, "Highly Reliable Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> Double Dielectric Films on Poly Crystalline Silicon" Extended Abstracts of the 19<sup>th</sup> Conference on Solid State Devices and Materials, Tokyo, 1987, pp.215-218.

- [3] Y. Ohji, T. Kusaka, I. Hiraiwa, K. Yagi, K. Mukai and O. Kasahara "Reliability of nano-meter thick multi-layer dielectric films on polycrystalline silicon," in 25<sup>th</sup> Annual Proc. Reliability Phys. Conf., 1987, p.55A.

- [4] H. Shinriki, Y. Nishioka, Y. Ohji, and K. Mukai, "Oxidized Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub> Dielectric Films on Poly-Crystalline silicon for dRAM's," IEEE Trans. Electron Devices, vol.ED-36, pp.328-332, 1989.

- [5] S. Kimura, Y. Nishioka, A. Shintani, and K. Mukai, "Leakage current increase in amorphous Ta<sub>2</sub>O<sub>5</sub> filims due to pinhole growth during annealing below 600°C," J. Electrochem. Soc., vol.130, p.2414, 1983.

- [6] Y. Nishioka, S. Kimura, H. Shinriki and K. Mukai, "Dielectric Characteristics of double layer structure of extremely thin Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> on Si, "J. Electrochem. Soc., vol.134, p.410, 1987.

- [7] Y. Nishioka, N. Honmma, H. Shinriki, K. Mukai, K. Yamaguchi, A. Uchida, K. Higeta and K. Ogiue "Ultra-Thin Ta2O5 Dielectric Film for High-Speed Bipolar Memories" IEEE Transactions on Electron Devices Vol.34, No.9, September p.1957, 1987.

- [8] Lee, J.C., Chen Ih-Chin, and Hu. Chnming, "Modeling and Characterization of Gate Oxide Reliability," IEEE Trans. Electron Devices, vol. 35, no. 12, pp. 2268-2278, Dec. 1988.

# 第4章 積層容量型 DRAM 用容量絶縁膜への Ta<sub>2</sub>O<sub>5</sub> 膜の適用

#### 4.1 緒言

多結晶シリコン上  $Ta_2O_5/SiO_2$  膜を、64 メガビット DRAM 用積層容量型メモリセル(STC CELL)の容量絶縁膜として検討する場合、以下の課題が挙げられる。

- (1) 多結晶シリコン電極上における  $SiO_2$  換算膜厚が 3 nm 相当の低欠陥、高信頼の  $Ta_2O_5$  膜を有するキャパシタの形成

- (2) 積層容量型メモリセル (STC CELL) などの立体化された容量部を有する DRAM への Ta<sub>2</sub>O<sub>5</sub> 膜を有するキャパシタの適用

- (3)  $Ta_2O_5$  膜を有するキャパシタの 16 メガビット DRAM プロセスで使用される高温プロセスへの適合性。