# Study on ambient gas effect in the annealing of ion-implanted GaAs toward realizing superior JFETs

(高性能 JFET 実現に向けたイオン注入 GaAs の

アニール時の雰囲気ガス効果に関する研究)

平成 25 年 9 月

奥洞明彦

## THESIS

# Study on ambient gas effect in the annealing of ion-implanted GaAs toward realizing superior JFETs

Akihiko Okubora

September, 2013

## Preface

The material of GaAs had inherently superior electronic properties, like extremely high electron mobility, large band gap, etc. However, the single crystal production technologies with excellent quality was not matured so that the controlling the crystal quality in the device fabrication process was quite important to extract the high potentiality of electronic properties. I was firstly in charge of the annealing of donor implanted GaAs toward the fully planar process GaAs FETs. The planer process was strongly recommended since it made followed interconnect formation process easier. The annealing temperature for the Si implanted GaAs attained to over 800 °C and the suppression of dissolution of the As atoms in GaAs surface during annealing was fatal issue. The semi-insulating property of the GaAs was thought to be a result of compensation of C<sub>As</sub> (C<sub>As</sub>; Carbon in As site) acceptor with EL2 (EL2; excess As related deep level ) deep donor. A main p-type contamination was thought to be a  $C_{As}$  and  $V_{As}$  $(V_{As}; Vacancy in As site)$  fostered  $C_{As}$  at that time. Therefore, if the dissolution of As was happened the Si-donor activation must be lowered by CAs accepter. I employed the annealing method for ion implanted GaAs using AsH<sub>3</sub> for excess As over pressure based on  $H_2$  carrier gas.

I was investigating the optimizing annealing condition for Si donor implanted GaAs in order to obtain higher activation day after day. The other day, I was noticed the difference between the C-V profiles of sample annealed in face-up method and that of face down method. The carrier profile annealed in face-up method is lower than that of face to face. In addition, the position of the profile of face-up method seemed to be slightly shifted to the direction of the surface. I felt this fact could not be explained by mere C<sub>As</sub> formation. Some thought stroke on my head that some interaction with annealing ambient must be occurred in the surface. Then, I tried to execute annealing using Ar as another inert gas to confirm my intuition. The results were quite worthy because the activation efficiency were over 90% even in face-up method. I decided to clarify this cause in order to obtain stable and reproducible annealing for GaAs FETs.

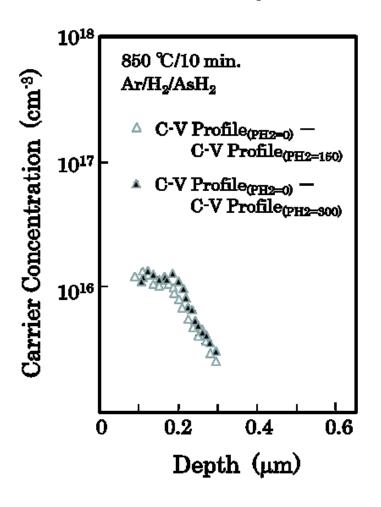

The experiments were start with the investigation about the influence of H<sub>2</sub> gas on the activation of implanted Si. It was found that the activation efficiency, especially in face-up configuration, was clearly depends on the partial pressure of H<sub>2</sub> gas in H<sub>2</sub> / Ar gas mixture ambient. The carrier loss distribution in H<sub>2</sub> gas ambient and face-up configuration was estimated by comparing the carrier profile of the sample annealed in Ar ambient with that in H<sub>2</sub> ambient. As a result of that, it was found that some carrier compensating center distributed in the depth of 0.1-0.4µm, at the peak concentration of  $1 \cdot 2 \times 10^{16}$  cm<sup>3</sup>.

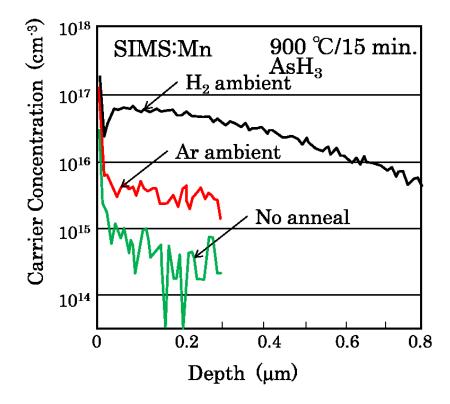

As far as this carrier compensation center, it was thought to be a kind of defects or impurities which were induced in GaAs during  $H_2$  ambient annealing. Firstly photoluminescence (PL) study was performed to investigate the origin of the carrier compensation. The properties of GaAs crystal at that time were thought to be a quite unstable in high temperature annealing and redistribution of many kinds of defects or impurities were reported. PL study was quite effective to identify the origin of carrier compensation since the depth of high sensitive region for PL study just coincided with that of carrier compensator. The Mn acceptor with activation energy of 100 meV was detected corresponding to  $H_2$  partial pressure. In order to clarify the quantitative validity of Mn<sub>Ga</sub> accumulation, SIMS analysis with step sputtering was performed under the cooperation of 'Surface Analysis Technology Gp' in SONY Research Center. As a result of that, the Mn<sub>Ga</sub> accepter was detected in almost same amount and same depth of carrier compensator obtained by C-V measurement. Thus, the cause of lower carrier activation in Si-implanted GaAs in H<sub>2</sub> gas annealing was found to be due to Mn<sub>Ga</sub> accumulation in the GaAs surface. However, it was still unclear that where the Mn derived from and what was the mechanism of Mn accumulation. Therefore, I determined to investigate the direct interaction of GaAs surface with H<sub>2</sub> gas like an 'etching phenomena'.

The experiments were performed to observe the difference of surface between uncovered region and covered region by protection film on the Si-implanted GaAs surface. The surface after annealing showed clear 'step' at the border between uncovered and covered region and this means 'etching' took place. The etching rate was found to be 1.0 - 1.5 nm / min. by measuring using 'Taly-step' and it was not depend on whether Si was implanted or not. In addition, the etching rate was proportional to the power of 2 third of  $H_2$  partial pressure and not depended on the AsH<sub>3</sub> partial pressure. The activation energy of the etching was estimated to be 2.90 eV and it corresponded to the evaporation of Ga and that the surface after annealing showed mirror-like one. These results strongly implied that GaAs surface in the high temperature annealing under H<sub>2</sub> ambient was etched by H<sub>2</sub> gas congruently. Furthermore, this etching phenomenon was found to be cause of the Mn accumulation in the surface of GaAs. As far as the origin of the Mn itself it was concluded that it must be derived from not the outer contaminations but the bulk substrate existing as residual impurities because the extent of the accumulated Mn was deeply dependent on the lot or supplier makers of the GaAs wafer. This new finding impacted on not only the other electronic device fabrication process but also photonic devices fabrication like laser diodes since H<sub>2</sub> ambient had been used commonly and widely in the annealing or epitaxial growth process in order to avoid the oxidation at the surface.

Further details for the mechanism of Mn accumulation at the GaAs surface were studied by using semi-insulating GaAs substrate without Si ion implantation. The samples annealed in only  $H_2$  ambient with or without AsH<sub>3</sub> showed p-type conversion. The SIMS analysis showed Mn accumulation in p-type converted samples at almost same quantity with carrier concentration measured by C-V method. However, Si atoms over the quantity of Mn were detected at the same time and the distribution of Si was quite similar to that of Mn. Normally, Si dopant in GaAs was said to occupy Ga site and to be Si<sub>Ga</sub> as a donor although it was amphoteric atom. Although the Si must be related to the Mn accumulation from the similarity of the distribution profile of Mn and Si, Si should be no contribution for the conductive type. This fact required the Si must be an interstitial site or self-compensated by equivalent quantity of Si<sub>Ga</sub> and Si<sub>As</sub>. Therefore, it was to be a key issue to understand the mechanism of Mn accumulation that how the Si dopant behaved in GaAs during the high temperature was revealed.

The analysis method using 'channeling effect' in the crystal like RBS or PIXE is quite useful to know the crystallography or the occupied site of the impurities. I thought to utilize these analyses to investigate the occupied site determination of implanted or not implanted Si in GaAs. The collaboration with Professor Abe group in Hokkaido University was started since they had an ion accelerator of Vande Graff type and already reported so many good works in this field. It was concluded that the detected Si was not in interstitial site and Si seemed to be self-compensated by the site-transfer in the case with excess annealing. As a result of above experiment, the mechanism of Mn accumulation was thought to be a result of inter-diffusion in donor-accepter duplicated pair, for instance  $Mn_{Ga}(-) - Si_{Ga}(+) - Si_{As}(-)$ .

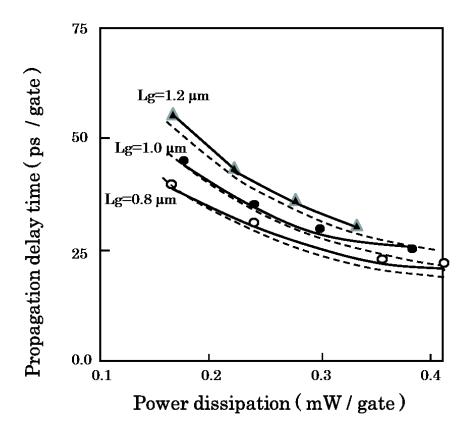

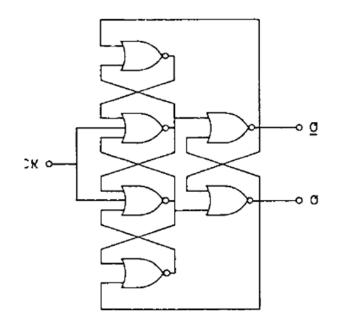

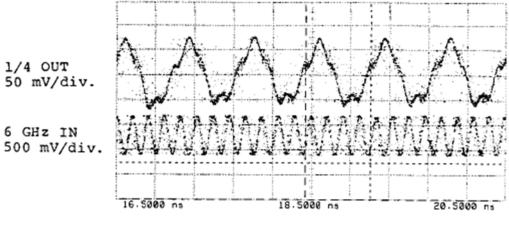

I established the new annealing method using Ar gas based ambient under the consideration of the disadvantages in H<sub>2</sub> gas ambient described above. The development of superior JFET was largely accelerated because reproducibility remarkably improved and also the turnaround time was effectively shortened by the annealing in face-up configuration. Especially, the dispersion of Vth in fabricated JFET in whole wafer and wafer to wafer was drastically improved. This fact was well explained by the suppression effect of the impurity re-distribution in Ar based annealing. This improved dispersion in Vth of JFET allowed the integration of large scale circuit. The maximum trans-conductance of 650 mS / mm and cut-off frequency of 65 GHz were accomplished. These were a level of worldwide record at that time. At the same time, the small scaled test circuit of a divide-by-four static frequency divider was fabricated and it proved the high potentiality of GaAs JFET by the operation at 6 GHz at the power consumption of 20 mW / flip-flop.

I faced so many difficulties and issues regarding the development of ICs, however, these were resolved one by one. These were, for instance, how to shorten the gate length, how to control the Vth in Zn diffusion process, how to fabricate the Au based interconnect without damages, etc. After the GaAs JFETs developments in research center the technology was transferred to the business section. Firstly GaAs JFETs applied to the digital IC applications and some products were shipped. The demand for the ICs in the RF frontend of cellular phones was raised up meanwhile the fabrication processes of GaAs JFETs were sophisticated. So many designers who had a skill for RF circuit joined to me and a RF switches IC, a low noise amplifier and a power amplifier were started to develop. The good uniformity and the superior reproducibility with good cost effectiveness of GaAs JFETs were largely useful in these products development. Especially, simple plus voltage operation which was enabled by large forward bias of JFETs satisfied customer's demand so that the analog application of JFETs could took off favorably. Finally, I would like to describe that my work contributed in no small way to the success in GaAs IC business.

# Contents

| Preface  | iii |

|----------|-----|

| Contents | vii |

#### <u>Chapter</u>

| 1.       | Introduction1                                                                 |

|----------|-------------------------------------------------------------------------------|

|          | 1.1 Aspects of GaAs devices for high-frequency and high speed<br>applications |

|          | 1.2 A viewpoints of this work2                                                |

| 2.       | Backgrounds4                                                                  |

|          | 2.1 Basic properties of GaAs4                                                 |

|          | 2.2 A theory for FETs and ICs7                                                |

|          | 2.3 Issues for the superior electronic device9                                |

| 3.       | Previous work for ion implantation and annealing of GaAs11                    |

|          | 3.1 Ion Implantation in GaAs11                                                |

|          | 3.2 Cap Annealing and capless annealing11                                     |

| 4.       | Ambient gas effect on activation of Si ion-implanted GaAs17                   |

|          | 4.1 Sample preparation17                                                      |

|          | 4.2 Influence of the carrier ambient gas17                                    |

|          | 4.3 Impurity pile-up on the surface21                                         |

|          | 4.4 Etching phenomena25                                                       |

|          | 4.5 Discussion about etching mechanism                                        |

| <b>5</b> | Thermal conversion in un-doped GaAs35                                         |

|          | 5.1 Electrical properties in thermally treated un-doped GaAs35                |

|          | 5.2 SIMS analysis in thermally converted samples                              |

| 6.       | Crystallographic studies by RBS/PIXE40                                        |

|          | 6.1 Basics in RBS and PIXE analysis40                                         |

|          | 6.2 Properties of Si dopant in annealing process                              |

| 7.       | A new annealing method and evaluation of fabricated FETs and ICs52            |

|          | 7.1 Proposed new annealing method                                             |

| 7.2 Basic characteristics evaluated by FAT-FET5                                       | <b>2</b> |

|---------------------------------------------------------------------------------------|----------|

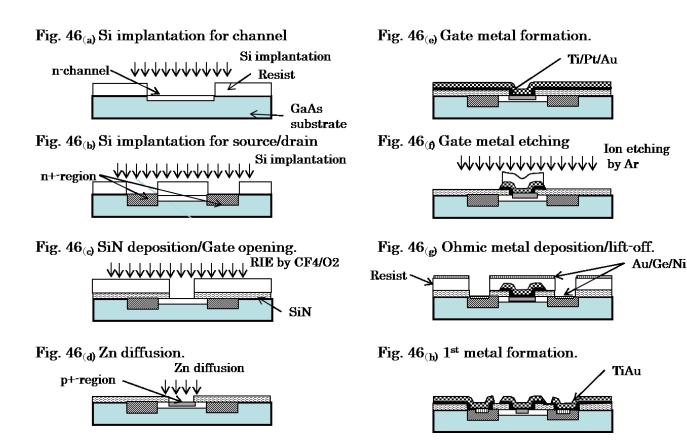

| 7.3 J-FET Fabrication Process5                                                        | 3        |

| 7.4 Evaluation results of high speed circuits5                                        | 7        |

| 9 Gummonu                                                                             | 0        |

| 8. Summary                                                                            | 0        |

| 9. Acknowledgement                                                                    | 52       |

|                                                                                       |          |

| References                                                                            | 3        |

| Appendix I. RBS/PIXE analysis on the out diffusion of Ga and As atoms into the cappin | ŋơ       |

| film of SiO <sub>x</sub> and SiN <sub>y</sub>                                         | 0        |

| this of Stox and Shty                                                                 |          |

# Chapter 1

## Introduction

# 1.1 Aspects of GaAs devices for high-frequency and high speed applications

The semiconductor technology evolution shows no signs of stopping or slowing down. This is represented by so-called 'Moore's Law' and realized under the basis of the 'scaling principle' in CMOS devices. However, recently, CMOS technology started to weaken by its physical limits or economical reason. Accordingly, it is strongly said that the evolution must be taken not the direction of scaled down CMOS but that of functional integration. This movement is called as 'More than Moore' and system level integration is targeted. Therefore, it is getting more important to integrate the devices which cannot be ruled over by the "scaling", these are high-speed devices in analog circuit, various kinds of sensors, passive components, MEMS devices and so on. These devices will add the wide functions of systems and open the way to realize new products.

In recent circumstance, III-V compounds semiconductor represented by GaAs devices are still playing an important role in electronic systems. These are already getting standard devices in almost all wireless or wired communication front-end systems of mobile or stationary products like a Smart Phone, Tablet PC, TV-set etc. These network based products require extremely high-band width in order to treat high quality videos like HD or x4K and various kinds of data so-called "Big Data". This circumstance requires explosive evolution and spread in network communication. In order to widen or make thicken the capacity of the network, multi-band and/or multi-mode communication technologies have been developed and made them in use. In addition, various kinds of multiple coding technologies are invented and they require higher frequency in the carrier to expand the band utility. In these progress, compounds semiconductor devices are getting indispensable in the frontend of wireless and wired communication systems such as the power amplifiers, switches and low noise amplifiers in the micro-wave or millimeter wave RF systems, and also, laser drivers, receivers and ultra-high speed serial-parallel converters in the optical communication systems. The main reason is coming from that their superior characteristics and performance cannot be realized by Si CMOS devices.

Regarding the superior characteristics of GaAs FETs, for instance, RF switches

[1], power amplifiers [2], high speed digital applications [3, 4] and optical front-end ICs [5, 6] are already reported. These characteristics are mainly brought by the high performance of GaAs FET itself and they owed originally developed JFET (Junction FET) with superior performance by using original diffusion and annealing technology in ion-implanted GaAs. In order to apply this devices to actual IC or LSI products, the uniformity, reproducibility and/or production capability are essentially important factors in the JFET fabrication process adding to the superior performance in discrete devices.

#### 1.2 A viewpoints of this work

The key factors to make success in consumer electronics are cost effectiveness and the performance. In order to achieve cost effectiveness, reproducibility, uniformity and productivity is especially important to raise the yield in fabrication process. In order to get superior performance, formation of shallow channel with higher carrier concentration in the FET is conclusively important as described in Chapter 2.2. The most simple and convenient method to make the active layers in the GaAs MES FET or JFET is ion-implantation and/or diffusion technique. These processes normally accompany high temperature treating above 600 °C - 900 °C. Therefore, thermal stabilities or properties of induced dopants, impurities, host atoms and/or various kinds of defects are essential concerns.

In addition, although the GaAs material is inherently having excellent electronic properties as described in Chapter 2.1, it is very difficult to control a stoichiometry in III-V compounds during the thermal treatment in the fabrication process since the each thermal properties of Ga and As is much different. As described in Chapter 3, various kinds of ideas or trials have been executed for the stoichiometric control of GaAs in the high temperature treating. However, unexpected carrier reduction or no reproducible incidents sometimes occurs. Therefore, it is fatal issue in so long time to realize excellent annealing method with no reduction in carrier activation and no diffusion in the interface between channel and bulk GaAs substrate.

Furthermore, it is also fatal issue to realize the excellent uniformity in FET characteristics in order to obtain the large scale integration with good yield. The GaAs substrate has a relatively large distribution of the defects or impurities that is induced in crystal growth process. These un-uniformity factors largely affect the deviation of FET characteristics, therefore, it is also fatal issue to suppress the redistribution of defects or impurities.

In this paper, I would describe the effect of annealing ambient in the donor activation process of ion-implanted GaAs. And then, it will be clarified by using the electrical analysis (Hall measurements and C-V measurements), optical analysis (photoluminescence) and physical analysis (SIMS analysis and Q-mass analysis). In succession, the mechanism of the carrier compensation or redistribution is discussed by using the crystallographic analysis (RBS/PIXE method). On the basis of these findings, I proposed a new annealing method in the JFET fabrication. Finally, the superior JFETs with good uniformity are obtained and the superior high-speed operations are achieved in the high-speed test circuit fabricated by using the newly established annealing method I proposed.

# **Chapter 2**

# Backgrounds

#### 2.1 Basic properties of GaAs

The basic GaAs characteristics compared with Ge and Si are shown in Table 1. The electrical and thermal characteristics of Si are excellent as shown in the Table 1, therefore, Ge transistor is replaced by Si. On the other hand, the main superior points in GaAs are higher electron mobility, larger band gap and so on. These are derived from its direct transition band structure. We should notice the each hole

| Table 1 | Important properties of Germanium (Ge), Silicon (Si) and Gallium Arsenide |

|---------|---------------------------------------------------------------------------|

| (GaAs)  | by A.S. Grove [7].                                                        |

| Materials                                          | Ge                         | Si                          | GaAs                |

|----------------------------------------------------|----------------------------|-----------------------------|---------------------|

| Atomic or molecular weight                         | 72.6                       | 28.09                       | 144.63              |

| Atoms or molecules /cm <sup>3</sup>                | $4.42 \times 10^{22}$      | $5.00	imes10^{22}$          | $2.3 	imes 10^{22}$ |

| Crystal structure                                  | Diamond                    | Diamond                     | Zinc-blende         |

| Lattice constant (nm)                              | 5.66                       | 5.43                        | 5.65                |

| Density (g/cm <sup>3</sup> )                       | 5.32                       | 2.33                        | 5.32                |

| Energy gap (eV)                                    | 0.67                       | 1.11                        | 1.4                 |

| Effective density states                           |                            |                             |                     |

| Conduction band (cm <sup>3</sup> )                 | $1.04 	imes 10^{19}$       | $2.8	imes10^{19}$           | $4.7 	imes 10^{17}$ |

| Valence band (cm <sup>3</sup> )                    | $6.0 	imes 10^{18}$        | $1.04 	imes 10^{19}$        | $7.0 	imes 10^{18}$ |

| Intrinsic carrier concentration (cm <sup>3</sup> ) | $2.4 \times 10^{18}$       | $1.45 	imes 10^{10}$        | $9 \times 10^{6}$   |

| Intrinsic mobility (cm <sup>2</sup> /v sec)        |                            |                             |                     |

| electron                                           | 3900                       | 1350                        | 8600                |

| hole                                               | 1900                       | 480                         | 250                 |

| Dielectric constant                                | 16.3                       | 11.7                        | 12                  |

| Melting point (°C)                                 | 937                        | 1415                        | 1238                |

| Vapor pressure (Torr)                              | 10 <sup>-7</sup> at 880 °C | $10^{\text{-5}}$ at 1250 °C | 1 at 1050 °C        |

| Specific heat (joule/g °C)                         | 0.31                       | 0.7                         | 0.35                |

| Thermal conductivity (watt/cm °C)                  | 0.6                        | 1.5                         | 0.81                |

| Coefficient of thermal expansion<br>(1/ °C)        | $5.8 	imes 10^{-6}$        | $2.5 	imes 10^{-6}$         | $5.9 	imes 10^{-6}$ |

mobility in Ge, Si and GaAs. The hole mobility of the GaAs is relatively smaller than that of Ge and Si so that the p-channel FET in GaAs is almost not developed so far. This fact means the complementary circuit like a Si CMOS cannot be realized in GaAs FET. This is one of the reasons that GaAs ICs do not target the low power digital ICs or LSIs.

As far as thermal property is concerned, a thermal conductivity and specific heat is also smaller than that of Si. In addition, vapor pressure in high temperature is much higher than that of Si and Ge as an order of 10<sup>5</sup>. This is much different point with Si and this means meticulous attention must be paid for desorption of GaAs host atoms in the high temperature treatment. This is the one of the main reasons for the difficulties in the fabrication process of GaAs FETs.

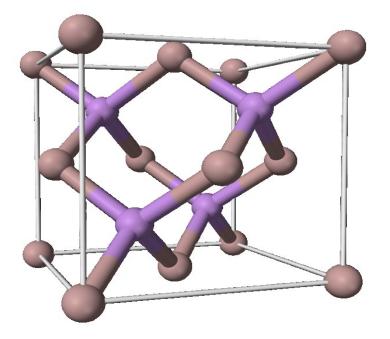

The crystal structure of GaAs is zinc-blende structure as shown in Figure 1. Normally, GaAs substrate is obtained by the cutting and the thinning of the ingot produced by using LEC (Liquid Encapsulated Czochralski) method or HB (Horizontal Bridgeman) method. In the LEC growing method, excess As is added into the PBN (Periotic Boron Nitride) crucible with Ga and As poly-crystal in order to avoid dissolution of arsenic molecular. It is well known that this excess arsenic atom formed the deep level (It is called as EL2) in GaAs, as a consequence, LEC grown GaAs shows semi-insulating properties [8, 9]. In the HB grown method, major contamination is Si shallow donor, coming from silica boat so that substrate shows inherently n-type. Cr metal, as a deep acceptor, is intentionally doped in order to obtain semi-insulating property.

Figure 1: GaAs Zinc-blende crystal structure.

This semi-insulating property is quite convenient for making ICs because there is no necessity to make isolation area. However, the semi-insulating properties cause some serious problems in thermal stabilities or electrical properties. As far as the electrical instability is concerned, high electrical field will be generated between the gate or source region and the neighbor drain region when the distance between the FET and neighbor FET is small. As a consequence, the region between the both transistor will be conductive by the carrier comes from the collapsed compensated state. This phenomenon is so-called 'side gating effect' or 'back gating effect' and the layout of each transistor must be paid much attention, otherwise proper isolation method must be required [10]. Regarding thermal stability issue, p-type or n-type conversion sometimes takes place at the surface of GaAs after the annealing over 800 °C. The origin of this type conversion is said to be the result of breaking of carrier compensation. N-type conversion at the surface in HB grown Cr-doped substrate, for instance, is said to be the results of Cr out-diffusion by thermal treatment [10]. P-type conversion in the un-dope LEC grown substrate is said to be the result of breakout of various kinds of compensation relation. P-type conversion especially in  $H_2$  ambient annealing is one of the issues in this paper and it will be investigated in detail and discussed in Chapter 6.

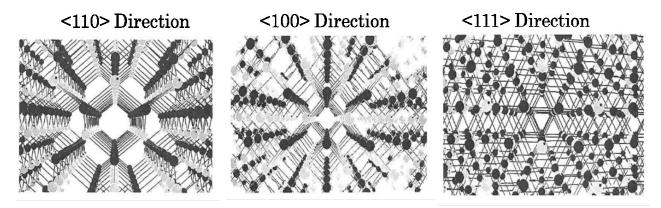

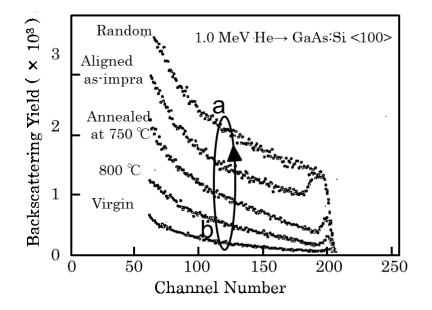

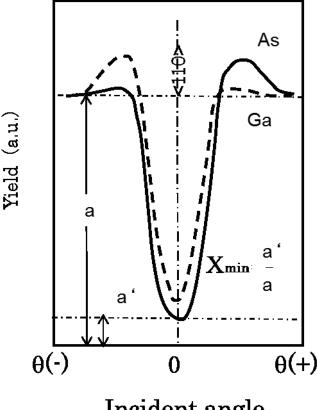

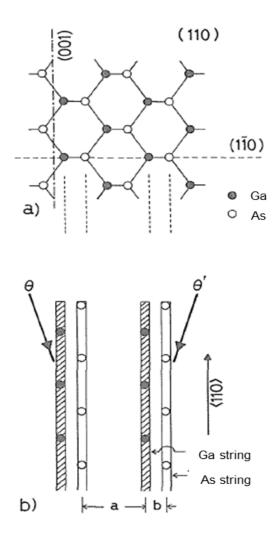

The properties of the thermal instability in the ion-implanted GaAs is more complicated than that of bulk semi-insulating GaAs. The lattice structure of the host crystal is destroyed into a disordered or an amorphous state. This means the various kinds of defects or dislocations must be induced by the ion-implantation process. Therefore, the crystal structure restoring process in the high temperature annealing after ion implantation is investigated by using RBS/PIXE analysis. These analyses are based on the nature of the 'channeling' in the crystal structure. A representative channeling views in the GaAs case is shown in Figure 2. The various kinds of information in crystal can be obtained by utilizing this channeling effect. The detail results are described in Chapter 7 and some important findings are revealed.

Figure 2: Perspective view in GaAs crystal from each direction.

#### 2.2 A theory for FETs and ICs

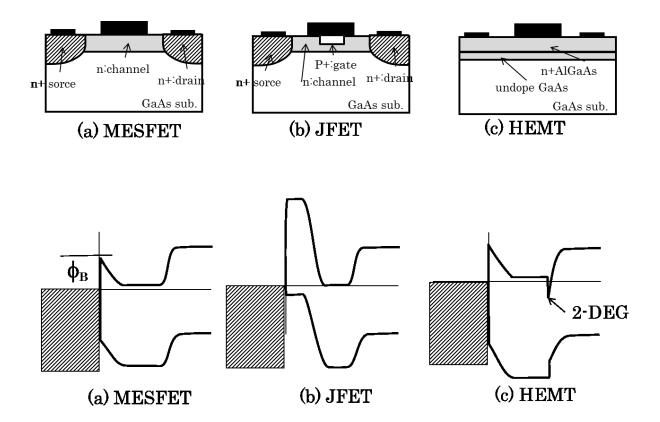

Various approaches to make MOS FET in GaAs have been investigated on the basis of Si MOS FET structure in the past. However, it has been found the oxidation with excellent quality in the GaAs surface is quite difficult to obtain. Therefore, different structures suit for GaAs properties are energetically investigated. These are MES FET, JFET and Hetero Structured FET. Schematic views of 3 types FET are shown in Figure 3(a), 3(b) and 3(c). The band diagram of each FET is likewise shown in Figure 4(a), 4(b) and 4(c). MES FET is most popular device in GaAs and the channel, source and drain region are normally formed by using selective ion implantation and annealing. The gate is structured by using Metal-Semiconductor Schottky barrier. The limits of the forward gate bias Vf is determined by the work function  $\phi_B$  of the gate metal as is shown in the Figure 4(a). The metal commonly used for MES FET is Al or Au and Vf is order of  $0.7 \sim 0.8$ V. This small Vf is to be a disadvantage when a large gain in the wide bias voltage range is required. In addition, cleanness of the surface and the damage-less fabrication process must be taken care to obtain the good and stable Schottky gate.

Figure 4: Band diagram of representive GaAs FETs.

On the other hand, JFET structure is also proposed in order to overcome the weak points of MESFET. The gate structure bases on a p-n junction, therefore, we can obtain larger Vf up to band-gap energy of 1.4 eV in the GaAs case as shown in Figure 4(b). The formation technology of p-type layer is one of the key issues. The stable formation of p-type layer using Zn diffusion into the Si implanted n-type GaAs substrate is already achieved under the arsenic overpressure by M. Dosen [12]. The Vf of the JFET is about 1.4V, therefore, high gain in the wide bias voltage is possible. At the same time, enhancement mode FET operation with high gain can be easily achieved in the JFET structure. It means that circuit operation in only + voltage power supply is possible and this will be a large advantage for the consumer products application. This advantage is to be one of the key factors to win the business in the RF-applications like RF switches or amplifiers.

As far as a hetero structured FET concerned, so many kinds of hetero FETs have been investigated and proposed. The most important device is a so-called HEMT (High-Electron Mobility-Transistor) based on an Al<sub>0.3</sub>Ga<sub>0.7</sub>As/GaAs hetero interface. The composition of 0.3 in Al and 0.7 in Ga is chosen as Al<sub>x</sub>Ga<sub>y</sub>As lattice constant matched with that of GaAs. The evolution of the epitaxial growth technology like a MBE (Molecular Beam Epitaxy) or a MOCVD (Metal Organic Chemical Vapor Deposition) allows various kinds of the composition of not only the III-V compounds but also II-VI. The abrupt interface with good quality is obtained by the advanced crystal growth technologies mentioned above so that various kinds of artificial structure are accomplished like a 'Quantum Well' or 'Quantum Dot'. These artificial structures bring drastic improvement not only in the electrical properties but also the optical properties. The name of the HEMT is derived from the 2 dimensional electron gas (2DEG). The principle of the HEMT is explained as bellows. As shown in Figure 4(c) the triangle well is formed in the hetero interface of un-doped GaAs side, so that the carrier in the n-type AlGaAs is spill over into the triangle well. Marvelous high electron mobility is obtained in this structure by virtue of the avoidance of impurities based electron scattering. This structure can be applied to the composition of the various kinds of materials. Pseudmorphic HEMT consists of AlGaAs/InGaAs/GaAs structure, for instance, is a representative device which is using the effect of intentional strain in the channel. This strain induces the breakout of degeneration in valence band structure so that the hole mobility can bring up. However, a reliability or thermal stability of the strained channel is thought to be one of the issues [13].

By cooling down to 77 K the electron mobility raises over 200,000 cm / sec [14], therefore, HEMT devices well match with ultra-low noise applications like a radio telescope or aero-space communications. On the other hand, these devices are not to

be commonly used in the consumer products by means of complicated fabrication process like an additional isolation process and necessity of cooling in the use of superior operation.

Therefore, the JFET is selected and developed as a candidate for the basic FET for ICs. However, the findings or results described in this paper, of course, can be applied to fabricate other kinds of FETs and ICs.

#### 2.3 Issues for the superior electronic device

In this chapter the structural requirements will be discussed from the viewpoints of realizing a superior performance in the JFET. In the performance of FETs one of the representative figures of performance is  $f_{\rm T}$  ( $f_{\rm T}$ ; cut off frequency).  $f_{\rm T}$  indicate maximum frequency limit of operation, and it will be written as;

$f_{\rm T} = 1/2\pi T$

$= v_{eff} / 2\pi Lg$

$= G_{\rm m} / 2\pi CgWgLg \tag{1}$

Here,  $G_m$  is a trans-conductance and indicates a rate of variability of drain current toward the gate bias voltage and  $v_{eff}$  is an average velocity of electron. Lg=gate length, Wg=gate width and Cg is capacitance around the gate, normally, Cg=Cgs (capacitance between gate and source electrode) + Cgd (capacitance between gate and drain electrode). Therefore, the meaning of the equation (1) is  $f_T$ corresponds to a reverse of the flight time of electron in the channel or charging time of the Cg by the drain current. Normally  $G_m$  is represented by using  $G_{mi}$  and Rs as follows;

$$G_{\rm m} = G_{\rm mi} / (1 + G_{\rm mi} Rs) \tag{2}$$

Here,  $G_{mi}$  is an intrinsic trans-conductance and it means a kind of conductance between the channel and source electrode region and Rs is a resistance in source region. From the equation, it is easily understood that higher  $G_m$  and lower Cgbrings superior high frequency performance. In order to obtain higher  $G_m$ , higher carrier concentration and electron mobility in the channel of FET are essentially required.

Furthermore, the  $G_m$  is also expressed by below equation from the Shockley JFET model [7];

$$G_{\rm m} = W_G * \mu * \varepsilon (V_G \cdot V_{th}) / L_a * L_G \tag{3}$$

Here,  $L_a$  = channel thickness,  $\mu$  = electron mobility,  $\varepsilon$  = dielectric constant of the GaAs,  $V_G$  = gate bias voltage and  $V_{th}$  = threshold voltage.

This implies that the carrier distribution in the channel must be shallow and

peak concentration must be higher. This fact means that we have to obtain the shallow and the highly activated channel without any carrier compensation through the ion implantation and the annealing. Although the various kinds of thermal treatment are experienced in the JFET fabrication process as described in Chapter 7.2, especially, the annealing for the activation of implanted Si donor is the highest temperature process. The annealing temperature normally attain to over 800 °C, so that the dissolution issues at the surface of GaAs should be maximally taken care. In the next Chapter, previous works for ion implantation and annealing in GaAs are explained and the difficulties in each annealing methods will be described with its reason.

## Chapter 3

# Previous work for ion implantation and annealing of GaAs

#### 3.1 Ion implantation in GaAs

Generally speaking ion-implantation technology is so often used for semiconductor devices. Important factors are implantation energy and dose and the dopant distribution profile. The dopant profile is to be a Gaussian distribution if the host material is homogeneous substance as is calculated by LSS (Lindhard, Scharff, Schiott Theory) theory [15]. The incident angle of ion beam must be selected as avoiding the channeling direction in order to obtain the stable and reproducible distribution of the dopant. As described in Chapter 1 (100) oriented surface is normally used for GaAs substrate so that the substrate is set with some tilt and rotate angle during ion implantation in order to avoid the channeling effect [16]. The energy level of the various kinds of dopants in GaAs is already investigated and summarized well in detail by S. M. Sze [17]. Si or Se is normally used as n-type dopant and C, Zn, or Be is used for p-type dopant. In this paper all the experiments are performed by using Si as a n-type dopant within the energy range of 60 keV - 160 keV and in the dose range of  $10^{12}$  cm<sup>-2</sup> -  $10^{16}$  cm<sup>-2</sup>. The implantation energy and the dose are changed as matching with purpose of each experiment. It is a main reason for using Si dopant that Si is a relatively stable during annealing and also has a no toxic characteristics. After Si implantation into the GaAs substrate an annealing is performed. The implanted Si re-distributes in the GaAs substrate affecting by the various conditions in the annealing. These affecting factors are, for instance, annealing temperature, time, ambient, heating method, heating rate, a configuration for setup, and so on. The activation ratio is defined by the ratio of the  $Si_{Ga}$  (Si in Ga site) to the whole implanted Si.

#### 3.2 Cap annealing and capless annealing

It is well known that 'Cap Annealing' and 'Capless Annealing' are investigated in order to avoid the dissolution of GaAs in the high temperature annealing. In the 'Cap Annealing', Si<sub>3</sub>N<sub>4</sub>, SiO<sub>2</sub> or SiN<sub>x</sub>O<sub>1-x</sub> films are typically used as a protection layer [18].

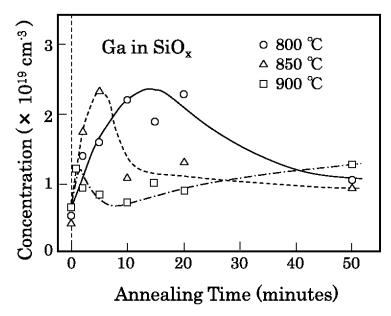

The cap layer is normally deposited after Si donor implanted by low temperature plasma CVD (p-CVD) method in the temperature range of 300 - 400 °C. This capped GaAs substrate is annealed in the N<sub>2</sub>/H<sub>2</sub> or Ar/H<sub>2</sub> mixture gas in the temperature range of 800 - 950 °C. Unless the quality of the protection layer is void-less and non-defective, a pealing or a cracking of protection layer takes place so often. The protection films of SiO<sub>x</sub> or SiN<sub>y</sub> have a residual stress at the interface with GaAs surface so that it causes sometime unexpected diffusion of the dopant and/or host

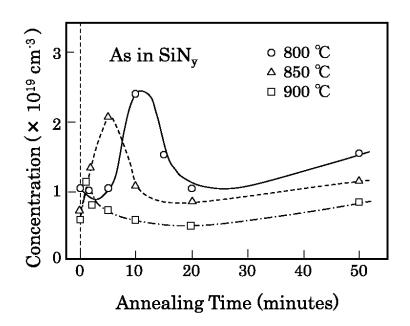

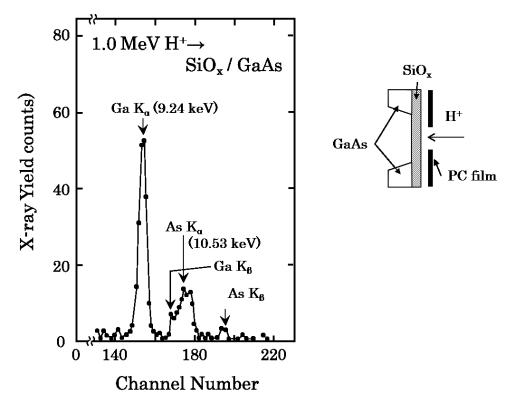

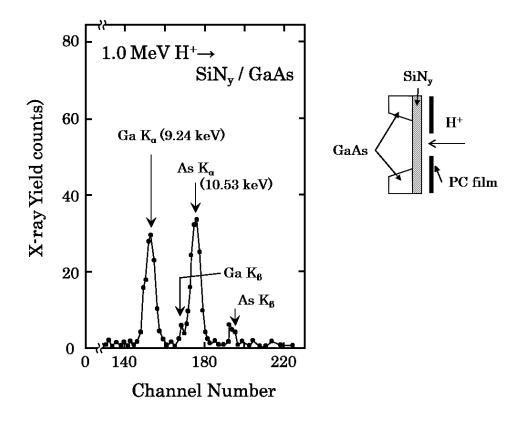

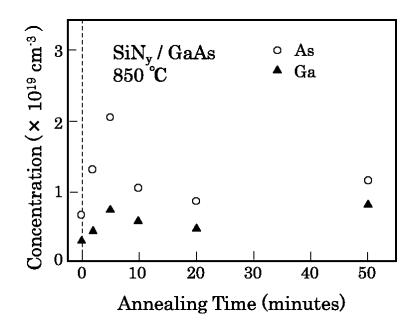

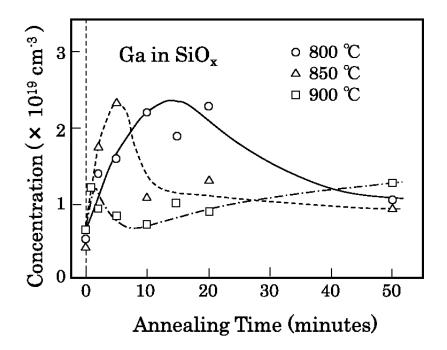

Figure 5: Residual Ga atoms in SiO<sub>x</sub> films as functions of annealing time and temperature.

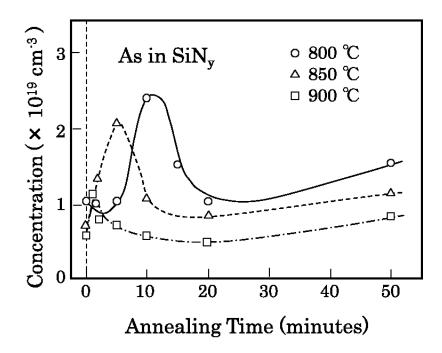

Figure 6: Residual As atoms in SiN<sub>y</sub> films as functions of annealing time and temperature.

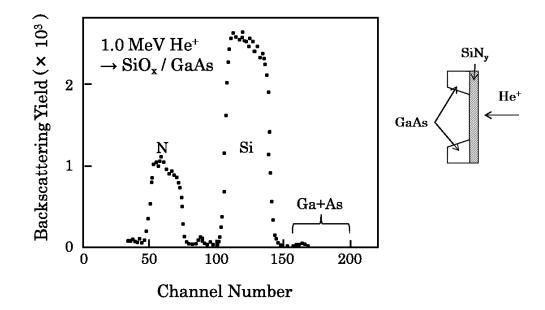

atoms. The quality of the protection film can be controlled by controlling the quantity of hydrogen atoms which is incorporated in the p-CVD process. However, it is found that the Ga or As atoms diffused into the protection films during the annealing even if the good quality in the protection layer obtained. In addition, the damaged layer in surface is induced by the film deposition process resulting in the anomalous diffusion takes place in the protection layer [19]. Here, only the results of out-diffusion introduced in Figure 5 and 6. For the details about this out-diffusion phenomena please see the APPENDIX I. Although it is remarkable results, the Ga out-diffusion in SiO<sub>x</sub> film mainly occurs, on the contrary, the As out-diffusion in SiN film mainly does. Figure 5 shows the results of out-diffusion of Ga in SiO<sub>x</sub> / GaAs system and Figure 6 shows that of As in SiN<sub>v</sub> / GaAs system evaluated by RBS/PIXE analysis. The properties of out-diffusion of each atoms are quite anomalous, namely, the quantity of residual host atoms of Ga and As in both films of SiOx or SiNy shows peaks in short annealing time. This peak goes away by the further annealing in time. These phenomena can be explained by the model that some damaged layer existing in GaAs surface will diffused into protect film at first, and then, the host atoms gradually out diffuse. The damaged layer is thought to be induced in the process of protect film deposition. The thermal CVD at 400 °C and the p-CVD at 350 °C are used for SiO<sub>x</sub> and SiN<sub>y</sub> film deposition, respectively. Therefore, a different kind of damaged layer is thought to be induced in each surface of GaAs. Thus the properties of out diffusion in capped annealing strongly affected by the state of interface in protect film and GaAs surface.

Furthermore, this capping layer give a residual stress for GaAs substrate especially near in the surface because the difference of thermal coefficient is large between capping layer and GaAs. This stress sometimes brings an anomalous

Figure 7: Schematic view of annealing apparatus.

Figure 8: Wafer set-up configurations.

diffusion of the implanted dopant. Thus this method is quite sensitive for the deposition condition of capping layer so that it is extremely difficult to archive a good uniformity and good reproducibility in the activation of the implanted dopant for GaAs.

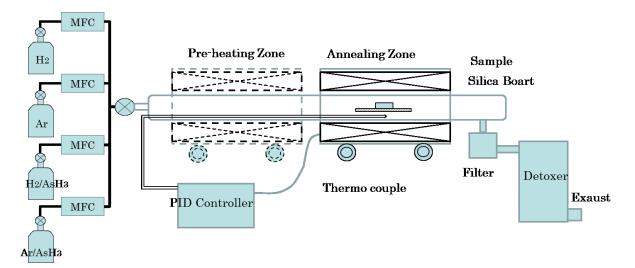

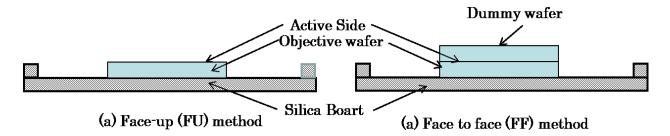

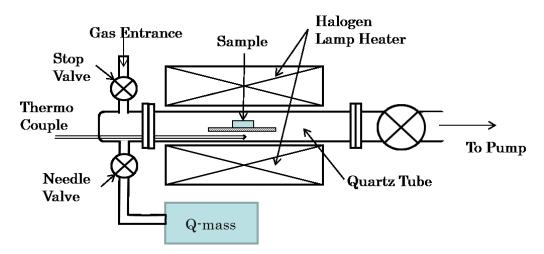

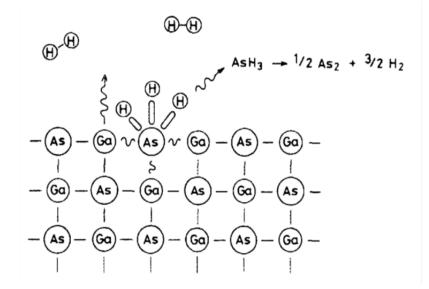

Therefore, the 'capless anneal' method is proposed by J. Kasahara et. al. [20] A capless anneal is performed in the As over pressure which is induced by  $AsH_3$  gas instead of the film protection. The induced  $AsH_3$  dissolved in the furnace into  $As_2$  and  $H_2$  perfectly resulted in As over pressure is applied. A schematic view of the annealing apparatus is shown in Figure 7. The furnace is on the rail and it can be move from the pre-heating zone to the annealing zone. An excess  $AsH_3$  or As is collect in the detox apparatus equipped at the end of the furnace. The temperature is controlled by PID controller by detecting the temperature using the thermocouple set inside in quartzes tube. The radius of the quartzes tube is about 12 cm and 2 or 3 inch GaAs wafer can be annealed. After ion implantation samples are set on a quartz boat horizontally with both holding configurations of Face-up (FU) and the Face to Face (FF) method. Here the FF method is a configuration that the objective wafer is covered with another GaAs wafer as illustrated in Figure 8.

An  $H_2$  ambient gas is chosen as a carrier gas since the surface of GaAs has to be protected from oxidation or contamination during high temperature annealing. The partial pressure of AsH<sub>3</sub> is determined by controlling the flow ratio of AsH<sub>3</sub> and H<sub>2</sub>. The typical partial pressure of AsH<sub>3</sub> is 3 Torr which is calculated under the assumption of total pressure is approximately 760 Torr because the furnace is open type.

The basic electrical properties are evaluated by using Van Der Paw method for Hall measurement and Hg Schottky probe method for C-V measurement after the annealing. The samples are cut into 5 mm<sup> $\Box$ </sup> under the consideration of wafer orientation. Indium dot of the order of 1 mm in diameter are put on the four corners of the samples and an ohmic contact is made by alloying in forming gas at the condition of 400 °C / several seconds.

In the typical annealing condition, as is 100 % H<sub>2</sub>/AsH<sub>3</sub> annealing, activation

ratio is investigated in both configuration of Face-up and Face to Face. The used dopant for n-type is Si and the implantation with accelerate energy of 130 keV and with dose of  $3 \times 10^{12}$  cm<sup>-2</sup> are performed.

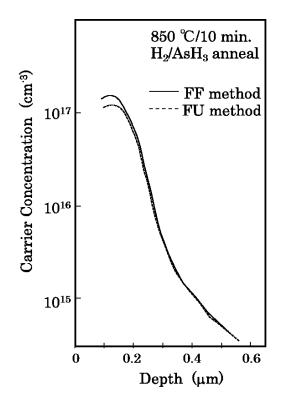

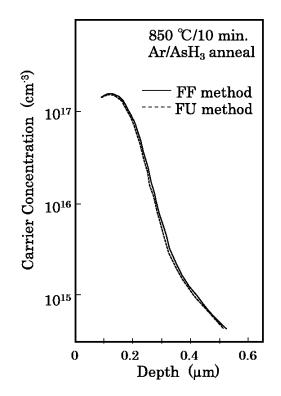

The electrical properties of sheet carrier density  $N_s$  (cm<sup>-2</sup>), sheet resistance  $\rho_s$  ( $\Omega/\Box$ ), Hall mobility  $\mu$  (cm<sup>2</sup>/V·sec) obtained by Hall measurement and calculated activate ratio are shown in Table 2. Activation ratio in Table 2 is calculated from the following C-V measurement by integrating the carrier profile. As easily understanding, the activation ratio with FU method is about 68 % and even that with FF method is 86 %. The difference between the FU method and the FF method is relatively large. The carrier profiles in both cases measured by C-V method are shown in Figure 9. The profile of FU configuration is explicitly low in peak and slender in depth than FF configuration. The annealing results in FF method should be avoided from the production cost because the twice quantity of GaAs substrate will be consumed at a once and the flexibility of the set up configuration like a vertically set-up batch processing must be lost.

The poor activation ratio, especially in FU configuration, is indicating some unexpected interaction between  $H_2$  and GaAs surface since the profile of FU configuration in Figure 9 is excessively slender than that of FF configuration. In order to investigate the cause of the lower activation ratio in  $H_2/AsH_3$  annealing, especially in FU method, carrier ambient gas dependency on the activation of Si in GaAs is carefully studied.

| Carrier Gas | Set-up        | P <sub>AsH3</sub><br>(Torr) | P <sub>H2</sub><br>(Torr) | $\rho s$<br>( $\Omega/\Box$ ) | Ns<br>(cm <sup>-2</sup> ) | $\mu (cm^2/V \cdot sec)$ | η (%) |

|-------------|---------------|-----------------------------|---------------------------|-------------------------------|---------------------------|--------------------------|-------|

| $H_2$       | FU            | 3                           | 760                       | $1.09 \times 10^{3}$          | $1.67 \times 10^{12}$     | 3611                     | 68    |

| $H_2$       | $\mathbf{FF}$ | 3                           | 760                       | $8.15 \times 10^2$            | $1.99 \times 10^{12}$     | 3893                     | 85    |

Table 2: Results of Hall measurement for the samples annealed in H<sub>2</sub> carrier gas.

$\label{eq:Figure 9} \begin{tabular}{ll} Figure 9 \\ \hline & Carierr \ profiles \ in \ H_2/AsH_3 \ annealing \\ measured \ by \ Hg \ probe \ C-V \ method. \end{tabular}$

## Chapter 4

# Ambient gas effect on activation of Si ion-implanted GaAs

#### 4.1 Sample preparation

The samples to be ion implanted are first degreased and chemically etched to remove native oxide and contaminations. The used samples are same as in Chapter 3.2, namely, the used dopant for n-type is Si and the implantation with accelerate energy of 130 keV and with dose of  $3 \times 10^{12}$  cm<sup>-2</sup> are performed. After ion implantation samples are set on a quartz boat horizontally with both holding configurations of Face-up (FU) and the Face to Face (FF) method. In order to investigate the ambient gas dependency, annealing experiments are performed under the condition of varying the partial pressure of Ar and H<sub>2</sub>. Specifically, the partial pressure is changed by changing a flow ratio of Ar and H<sub>2</sub>. Here, the total flow rate keeps at 0.5 l/sec. Typical annealing condition is 850 °C in anneal temperature and 10 minutes in anneal time. Not only the dependency of atmosphere but also that of annealing temperature, time and AsH<sub>3</sub> partial pressure is also investigated.

The basic electrical properties are evaluated by also using Van Der Paw method for Hall measurement and Hg Schottky probe method for C-V measurement.

#### 4.2 Influence of the carrier ambient gas

The Ar gas is chosen as a carrier gas because Ar is one of the inert gases and very popular as a forming gas. Furthermore, molecular weight of Ar is 40 and this is much closer to that of AsH<sub>3</sub> (molecular weight is 78) than H<sub>2</sub>. This means better gas mixture state is easily obtained. In addition, N<sub>2</sub> gas should be avoided because there is a possibility of direct reaction with GaAs since N<sub>2</sub> is a group V elements. The annealing with 100% Ar/AsH<sub>3</sub> ambient is executed and the results are shown in Table 3. It is easily understanding that the activation ratio of the Ar 100 % annealing is higher than that of H<sub>2</sub> 100 % especially in a FU configuration. This fact explicitly suggests that some interaction factors exist between H<sub>2</sub> gas and GaAs surface.

| Carrier Gas | Set-up        | P <sub>AsH3</sub><br>(Torr) | P <sub>H2</sub><br>(Torr) | ρs<br>(Ω/□)          | Ns<br>( cm <sup>-2</sup> ) | $\mu (cm^2/V \cdot sec)$ | η (%) |

|-------------|---------------|-----------------------------|---------------------------|----------------------|----------------------------|--------------------------|-------|

| Ar          | FU            | 3                           | 0                         | $7.33 \times 10^2$   | $2.12\times10^{12}$        | 4016                     | 91    |

| Ar          | $\mathbf{FF}$ | 3                           | 0                         | $7.01 \times 10^{2}$ | $2.17\times10^{12}$        | 4122                     | 96    |

Table 3: Results of Hall measurement for the samples annealed in Ar carrier gas.

The carrier distribution profiles by C-V measurement in the Ar cases are shown in Figure 10. The profile in Ar 100 % annealing shows a little bit higher peak carrier concentration and slightly fat in depth distribution than that of  $H_2$  100 % annealing. The difference in activation ratio between both samples is well explained by the difference between both carrier profiles. Furthermore, the fact that the activation ratio only in FU case of 100 %  $H_2$  annealing is prominently worse strongly indicates something happen in annealing of  $H_2$  atmosphere.

Figure 10: Carierr profiles in Ar/AsH<sub>3</sub> annealing

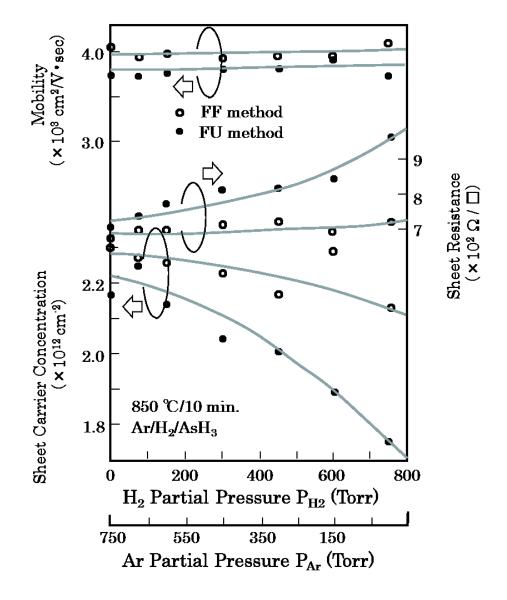

In order to investigate the effects of Ar ambient annealing the H<sub>2</sub>/Ar partial pressure in Ar/H<sub>2</sub>/AsH<sub>3</sub> annealing is intentionally changed. In all the experiments the partial pressure of AsH<sub>3</sub> keeps constant at 3 Torr and the partial pressure of H<sub>2</sub> is varied by changing the Ar mixture ratio in carrier gas with the both setting of FU and FF configuration. The measured electrical properties Ns,  $\mu$  and  $\rho_s$  are

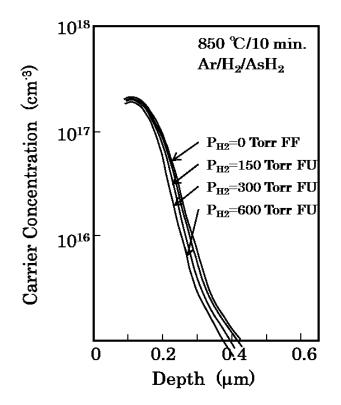

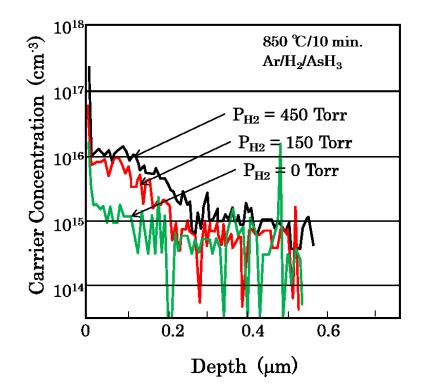

summarized in Figure 11. The Ns and  $\mu$  are increasing as the H<sub>2</sub> partial pressure is decreasing and the  $\rho_s$  is decreasing on the contrary. These facts apparently indicate the carrier reduction in activation is getting larger as increasing the partial of H<sub>2</sub> ambient. The carrier profiles change measured by C-V method is shown in Figure 12. The peak carrier concentration is getting smaller and the depth profile is getting slender according to the H<sub>2</sub> partial pressure increasing.

Figure 11:  $P_{H_2}$  dependency of Ns,  $\rho$  and  $\mu$  obtained by Hall measurement.

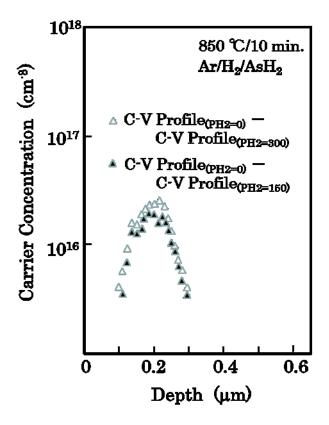

Net lost carrier concentration is calcul**a**ted by extracting the profile of the Ar annealing from that of the H<sub>2</sub> annealing. The results are shown in Figure 13 and it will indicate that there is something to be a cause of carrier lost existing near the surface. The peak concentration of the lost carrier is estimated about the order of 2 -  $3 \times 10^{16}$  cm<sup>-3</sup> and the depth attains to the order of 300-400 nm.

Figure 12:  $P_{H2}$  dependency of carrier profiles by C-V measurement.

Figure 13: Lost carrier distribution near the surface.

#### 4.3 Impurity pile-up on the surface

In order to investigate the cause of carrier lost near the surface photoluminescence studies are performed. If the cause of carrier lost is due to formation of some defect or a kind of impurities redistribution, photoluminescence study is adequately effective since the penetration depth of the excitation light is as same as the depth of lost carrier distribution. Photoluminescence study is executed in following conditions;

Ar Gas Laser at 514.5 nm is used as an excitation light source and photo multiplier (Hamamatsu Photonics Co.) is used as a light detector. The measuring temperature is determined to be at 4.2 K because the various structural change or luminescence from the re-combination center induced by some impurities should be de-convolved clearly.

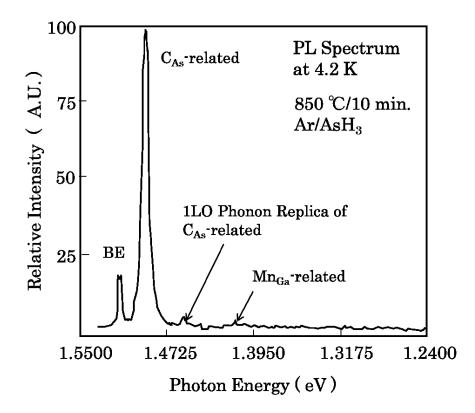

Firstly the photoluminescence spectrum measurement in the case of 100 %  $Ar/AsH_3$  ambient annealing is performed and the result is shown in Figure 14. The distinct luminescence peaks are seen around the energy level of 1.51 eV, 1.49 eV, 1.43 eV and 1.41 eV. The origin of the each peak is already investigated in detail [21, 22] so that the luminescence peaks around the 1.51 eV, 1.49 eV, 1.43 eV and 1.41 eV are identified as the band edge emission,  $C_{As}$  acceptor related emission, 1LO phonon replica of  $C_{As}$  related peak and  $Mn_{Ga}$  related emission respectively. The peaks around

Figure 14: Typical photoluminescense spectrum in Ar 100 % annealing.

Figure 15: Photoluminescence spectrum near band edge.

Figure 16: Photoluminescence spectrum near 1.49 eV.

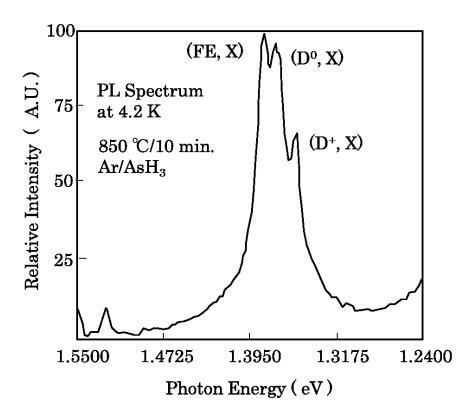

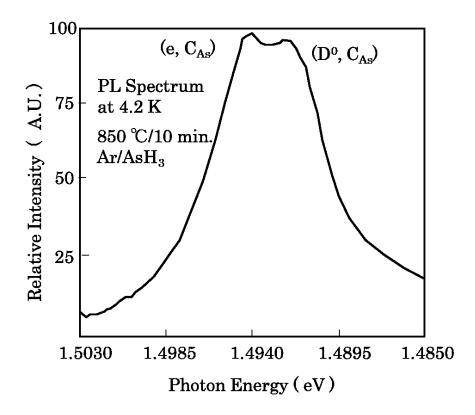

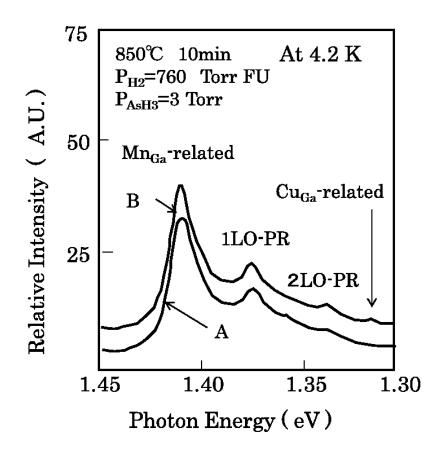

the 1.51 eV and 1.49 eV are enlarged in Figure 15 and 16, respectively. The peaks around 1.51 eV including 3 peaks at 1.5161 eV, 1.5152 eV and 1.5135 eV as shown in Figure 15. These peaks are exciton related peaks of (Free Exciton), (D<sub>0</sub>, Exiton), (D+, Exciton) respectively. The peaks near the 1.49eV also including 2 peaks at 1.4943 eV and 1.4924 eV as shown in Figure 16 and they are estimated to be  $C_{As}$  acceptor related peaks of (e,  $C_{As}$ ) and (D<sub>0</sub>,  $C_{As}$ ). In these luminescence peaks, the change of the peak of the  $C_{As}$  related and that of the Mn<sub>Ga</sub> related must be carefully looked at because the both are estimated to act as an acceptor in GaAs [16] and it will be a candidate of carrier loss.

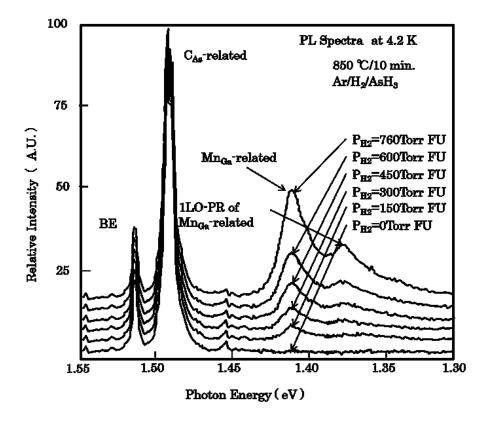

The  $H_2$  partial pressure dependency of the photoluminescence is investigated based on the basic luminescence properties identified above. The change of the photoluminescence property according to the changing of the  $H_2$  partial pressure is shown in Figure 17. The peaks around the 1.41 eV are drastically increasing as the partial pressure of  $H_2$  increasing. The peak at 1.412 eV of  $Mn_{Ga}$  acceptor as explained above accompanies 2 other peaks of 1.378 eV and 1.340 eV. They are estimated to be a 1LO phonon replica and 2LO phonon replica respectively. On the other hand, the luminescence from the  $C_{As}$  around 1.41 eV shows almost no change. This fact strongly suggests that Mn impurity at near the surface is increasing by  $H_2$  ambient annealing so that the implanted Si-donor must be compensated by  $Mn_{Ga}$  acceptor. Furthermore,  $C_{As}$  accepter and other kinds of defect related recombination centers

Figure 17:  $H_2$  partial pressure dependency of photoluminescence spectra.

seem to have almost no contribution in the surface carrier loss. However, these photoluminescence studies are not quantitative but qualitative.

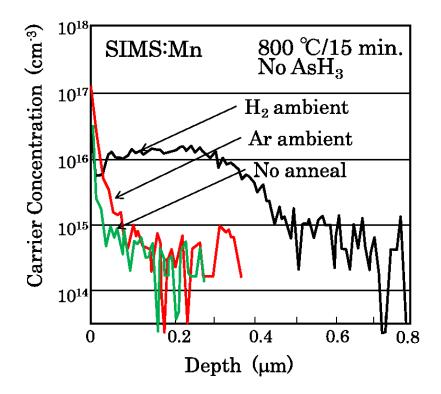

In order to clarify the quantitative estimation of the Mn acceptor contribution, direct observation of the Mn located near the surface is executed by using SIMS (SIMS: Secondary Ion Mass Spectroscopy) analysis. The depth profiles are easily obtained at the same time by using the sputtering. The SIMS apparatus is made of CAMECA corp., the model name is IMS-3F. The used first order ion source is O+ for the Mn distribution analysis. The standard samples made by Mn ion implantation are prepared to calibrate the results for the quantitative discussion.

The samples on the case with 0 Torr, 150 Torr and 450 Torr of  $H_2$  partial pressure are analyzed and obtained Mn profiles are shown in Figure 18.

Figure 18: Mn depth profiles dependency on  $H_2$  partial pressure at 850 °C / 10 minutes annealing measured by SIMS.

Although the X-axis inherently is a time scale which corresponds to the sputtering time it can be converted to depth scale easily by calculating the sputtering rate of O+ to the GaAs crystal. As for the Y-axis the relative intensity of detected ions is converted to concentration in the same way by virtue of the calibration using the Mn implanted standard sample. It is quite clear from the Figure 18 that Mn atoms are clearly piled up near the surface and it is increasing as the H<sub>2</sub> partial increasing.

The Mn is located in the depth range from the surface to 400nm and the peak concentration attains to the order of  $2 \times 10^{16}$  (atoms/cm<sup>3</sup>) in the case of 450 Torr in H<sub>2</sub> partial pressure. This value is quite similar to the lost carrier estimated from the difference from the C-V profiles but it might be not completely explained only by the Mn accumulation. It is doubtless that Mn, which acts as an accepter, is sure to accumulate near the surface in the H<sub>2</sub> ambient annealing and it will be a main cause of carrier loss [23]. However, it is still unclear about the origin of the Mn and how it can be piled up at the surface. As far as the origin of the Mn is concerned, whether the kind of contamination from the experimental environment or the impurity essentially incorporated in GaAs substrate itself should be clarified. At the same time what is the motive force of the Mn piling up only in H<sub>2</sub> ambient must be revealed.

By careful observation of the difference between the C-V profiles in Ar based annealing and that of  $H_2$  based annealing, the possibility of the etching in the GaAs surface is suggested. Therefore, whether the kind of etching happens or not in  $H_2$ based annealing is investigated.

#### 4.4 Etching phenomena

The samples used here are made by same conditions in Chapter 3.2, namely, samples are implanted with Si at the energy of 130 keV and a dose of  $3 \times 10^{12}$  cm<sup>-2</sup>. Additionally, the samples without ion implantation are also prepared in order to confirm the affection of with or without implantation. Half of the sample surface is covered with Si<sub>3</sub>N<sub>4</sub> film deposited by plasma CVD before annealing. Annealing is performed in a quartz tube in the temperature range from 850 to 925 °C exposing a

Figure 19: Schematic illustration for analysis of reacted gas by Q mass at 800 °C under the hydrogen pressure of 10 Torr.

sample surface to the gas flow in a FU configuration. A Taly-step is used to determine the etched depth after annealing in reference to the step between the region covered with  $Si_3N_4$  and the uncovered region.

In another experiment samples are heated to 800 °C by a halogen lamp heater. Gaseous products produced by the reaction of GaAs with the ambient gas are sampled through another quartz tube branch and analyzed with a quadrupole mass spectrometer (Q mass) which is schematically illustrated in Figure 19.

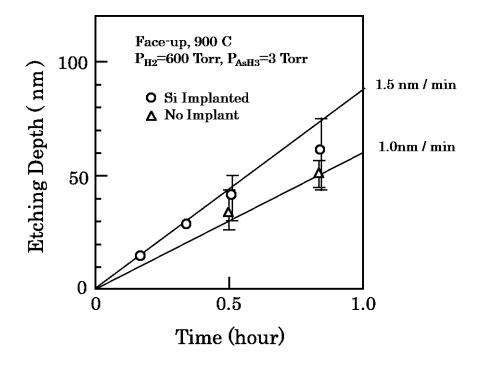

Etched depths are plotted in Figure 20 after annealing at 900 °C under the  $H_2$  partial pressure and AsH<sub>3</sub> partial pressure of 600 and 3 Torr, respectively. Open circles and open triangles represent the samples implanted with Si and not implanted, respectively. The two samples are etched essentially equally within experimental error. The etched depth increases linearly for the annealing time. The etching rate is  $1.1 \cdot 1.5$  nm / min at 900 °C and P<sub>H2</sub>: 600Torr. The etching rate did not depend on the flow rate of the mixture gas within the range from 0.825 to 3.3 l/min.

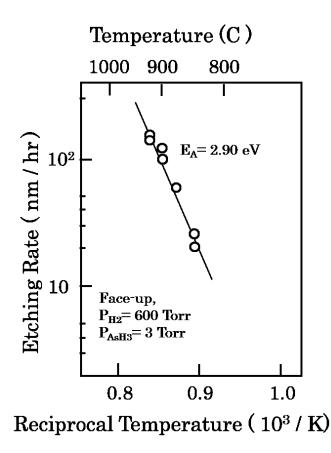

The temperature dependence of the etching rate is investigated in the temperature range from 850 to 925°C. The etching rate increases with increase of the annealing temperature under a constant partial pressure of  $H_2$  and  $AsH_3$ , of 600 and 3 Torr, respectively. The Arrhenius plot of the etching rate shown in Figure 21 indicates the activation energy of 2.90 eV, which agrees well with the heat of

Figure 20: Etching depth vs annealing time at 900 °C under the hydrogen pressure of 600 Torr and arsine pressure of 3 Torr. Open circles indicate Si implanted samples and open triangles indicate not implanted samples.

evaporation of Ga [24]. It can be concluded that the thermal etching of GaAs in an  $H_2$  ambient under excess arsenic pressure is governed by Ga evaporation [25].

The surface of the sample is smooth, and a mirror-like surface is preserved up to a temperature of 925 °C under excess arsenic pressure. It is indicating that Ga and As evaporated almost congruently by virtue of the suppression of desorption of volatile arsenic atoms under arsenic over pressure.

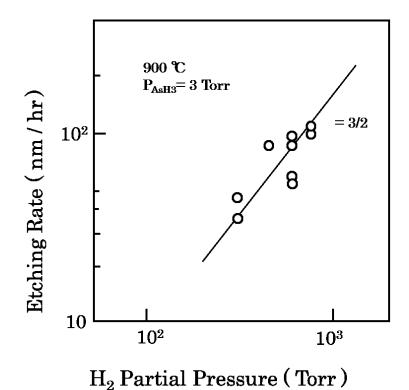

As described in Chapter 4.2, the Mn accumulation near the surface of GaAs is closely related to the partial pressure of H<sub>2</sub>. Therefore, etching rate dependency of P<sub>H2</sub> is quite important. The etching rate is plotted in Figure 22 as a function of P<sub>H2</sub>, under the condition of a constant temperature of 900 °C and P<sub>AsH3</sub> = 3 Torr. The etching rate increases with increasing P<sub>H2</sub>. It is found that the etching rate is approximately proportional to the 3/2th power of P<sub>H2</sub>. In fact, in Ar based annealing, which corresponds to H<sub>2</sub> based annealing of 0 Torr, there is no thermal etching at all.

Figure 21: Arrhenius plot of the etching rate under the condition of  $P_{H2}$ =600 Torr and  $P_{AsH3}$ =3 Torr.

Figure 22: Etching rate as a function of hydrogen partial pressure at 900 °C under the  $P_{AsH3}$ = 3 Torr.

AsH<sub>3</sub> Partial Pressure (Torr)

Figure 23: Etching rate dependence on  $AsH_3$  partial pressure under the  $PH_2$  of 600 Torr (O) and 300 Torr ( $\Delta$ ).

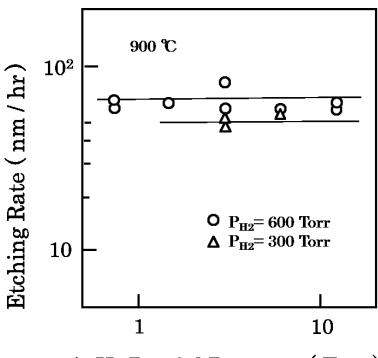

We also investigated whether varying the AsH<sub>3</sub> partial pressure would affect the etching rate. Annealing is performed at 900 °C under the conditions of  $P_{H2}$  = 600 and 300 Torr. The partial pressure of AsH<sub>3</sub> is varied from 0.75 to 12 Torr. No significant change in the etching rate is, however, observed either with  $P_{H2}$  = 600 or 300 Torr as is shown in Figure 23.

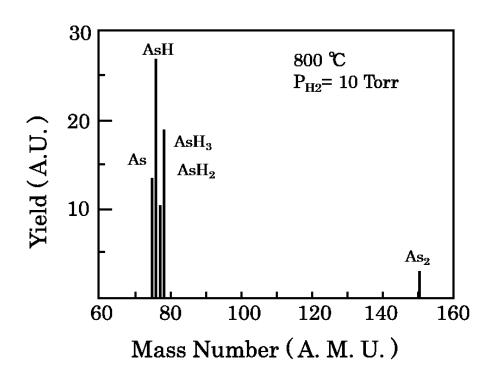

Gaseous species in a quartz reaction tube, during heat treatment of GaAs in  $H_2$  or Ar ambient, are directly analyzed by the quadrupole mass spectrometer. No AsH<sub>3</sub> is introduced in this experiment. Figure 24 is a typical mass analysis spectrum obtained during heat treatment in the  $H_2$  ambient, from which background spectrum is subtracted.

Arsenic (As+:75 amu), AsH family (AsH+:76 amu, AsH<sub>2</sub>+:77 amu, AsH<sub>3</sub>:78 amu) and As<sub>2</sub>+(150 amu) are observed in the spectrum. The arsine family must be due to an ionization process in the Q mass. On the other hand, no peaks are observed during heat treatment in the Ar ambient. There must be direct reaction of H<sub>2</sub> with

Figure 24: A mass spectrum of reacted gas during annealing in a 10 Torr hydrogen ambient at 800 °C.

Figure 25: PIXE spectrum in the wall of quartz near the sample.

Figure 26: PIXE spectrum in the wall of quartz far from the sample.

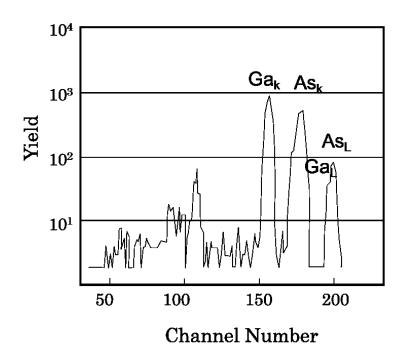

GaAs at high temperature and must be a gaseous product. No Ga-related peaks are observed during heat treatment both in the  $H_2$  and Ar ambient. Ga atoms are, however, detected on the wall of the quartz tube by an analysis using PIXE after the heat treatment in both of the ambient. However, detected Ga signal in Ar ambient is much lower than that in  $H_2$  ambient annealing. Furthermore, **G**a is only detected in the wall of quarts tube near the sample. This fact can be explained by the low vapor pressure of Ga so that the evaporated Ga abruptly quenched and is deposited in the cold wall near the sample. These results are shown in Figure 25 and Figure 26. These experiments are executed by detecting the characteristic x-ray emission from the Ga atoms although the basics about PIXE analysis will be explained in Chapter 6.1.

### 4.5 Discussion about etching mechanism

Generally, dissociation of GaAs at high temperature is governed by the reaction and expressed by

$GaAs \rightarrow Ga_{(s)} + 1/2 As_2$ (4) or  $GaAs \rightarrow Ga_{(s)} + 1/4 As_4$ (5)

Reaction (4) is dominant in the temperature range used in our experiments [26].

After annealing above 800 °C, thermal pits usually appeared at the surface of GaAs, leaving Ga droplets within the pits. No thermal pits are, however, observed in our experiment under arsenic overpressure. The surface of the sample thermally etches in  $H_2/AsH_3$  ambient is smooth, mirror-like and free from crystallographic defects, suggesting congruent evaporation.

The temperature at which congruent evaporation occurs is determined using Eq. (4) or (5) as 637 °C by Arthur [27], 660 °C by Thurmond [24] and 625 °C by Foxon et. al [28]. These temperatures are much lower than the lowest temperature in our experiments. Eq. (4) or (5) is unlikely to dominate dissociation of GaAs under arsenic overpressure. The AsH<sub>3</sub> flow, which is considered to decompose most perfectly into H<sub>2</sub> and As<sub>2</sub> at our experimental temperature [24], gives an As overpressure of 3 Torr. This As overpressure corresponds to about 2 orders of magnitude higher than the As dissociation pressure of  $1.5 \times 10^{-2}$  Torr of GaAs at 900 °C [27]. The fact that the annealing under the Ar/AsH<sub>3</sub> ambient reveals no etching means the As dissociation process, Eq. (4) or (5), is well suppressed by As overpressure. The smooth and featureless surface after annealing at temperatures above 800 °C also must be due to the As overpressure.

Based on our experimental findings that the activation energy for thermal etch agrees well with the heat of evaporation of Ga, that the rate of thermal etch is proportional to the partial pressure of  $H_2$  to the 3/2th power and that  $AsH_3$  is detected in the reaction tube during annealing, we propose as the etching mechanism the chemical reaction (6),

$$GaAs + 3/2H_2 \rightarrow Ga(s) + AsH_3.$$

(6)

This reaction is likely to occur because the bonding energy between H and As [29] is higher than that between Ga and As [30], AsH<sub>3</sub> [31] and PH<sub>3</sub> [32]. These bonding energy previously has been reported in the process of the reaction between atomic H and GaAs or InP at an elevated temperature. The pressure of AsH<sub>3</sub> to be expected by reaction (6) can be roughly estimated by the law of mass action and the quantity of As lost estimated by the etching depth. The estimated partial pressure of AsH<sub>3</sub> is as low as  $1.3 \times 10^{-8}$  Torr, which means that the estimated partial pressure of atomic H required for the reaction with GaAs is as low as  $4 \times 10^{-8}$  Torr. Fundamental chemical data says that more than  $1 \times 10^{-5}$  part of molecular H<sub>2</sub> decomposes to atomic H at the temperature considered [34]. It is strongly suggested that the kinetics involve the chemisorption of atomic H, as the first step, with subsequent reaction of H with As.

The law of mass action also tells us that the etching rate should depend on  $P_{AsH3}$ , which is inconsistent with our finding that the rate of thermal etching is independent of the partial pressure of  $AsH_3$ . This inconsistency is, however, resolved by the following reaction:

$AsH_3 \leftrightarrow 1/2 As_2 + 3/2H_2 \tag{7}$

Decomposition of AsH<sub>3</sub>, that is, the reaction rate from the left to the right, is much faster than the reaction rate from the right to the left at the temperature considered [26]. AsH<sub>3</sub> introduced into the reactor must be decomposed into As<sub>2</sub> and H<sub>2</sub> by reaction (7). The partial pressure of As<sub>2</sub> does not directly affect reaction (6), that is, the rate of thermal etching independent of  $P_{AsH3}$ . AsH<sub>3</sub> produced by reaction (6) also must be decomposed immediately after the reaction. Reaction (6) is the intermediate reaction, leading to the decomposition of GaAs into Ga and As<sub>2</sub>. A

Figure 27: A schematic model for the thermal etching of GaAs with  $H_{_9}$ .

mechanism for the thermal etch of GaAs with  $H_2$  is proposed in Figure 27. The difference in the characteristics after high-temperature annealing in the  $H_2$  ambient and the Ar ambient can be explained by the thermal etch.

GaAs surface is found to be etched by hydrogen above 800 °C. It is directly confirmed by a step which occurred after annealing at the boundary between the uncovered and covered region. The surface of the annealed GaAs is smooth, mirrorlike, and featureless when the thermal etching proceeded under arsenic overpressure, indicating that evaporation of Ga and As atoms take place congruently. The etching activation energy showed that thermal etching is governed by rate of Ga evaporation. The thermal etching is proportional to 3/2th power of P<sub>H2</sub>. AsH<sub>3</sub> is detected by Q-mass analysis of the gaseous products during annealing. Direct reaction of GaAs with hydrogen is confirmed by these experimental facts [34].

Although the etching is taken place in H<sub>2</sub> ambient and the etching mechanism is revealed, the origin of the Mn is still unclear. As known well, the raw material of GaAs crystal is extracted from the residual of copper mine. GaAs is a by-product of copper and the impurities, like a Mn, Cu is included at an order of  $10^{13} - 10^{14}$ atoms/cm<sup>3</sup>. Therefore, it is quite natural that Mn is coming from the substrate itself and piling up in the surface during annealing. Actually a photoluminescence peak of 1.31 eV is also observed. As shown in the Figure 28, origin of this peak is thought to be Cu related one, furthermore, the intensity is largely dependent with the GaAs wafer providing makers. In the Figure 28, spectra of the substrate provided by maker "A" shows the peak of 1.31 eV, however, it is not clear in the that of provided maker B. This strongly supports the same piling up mechanism in deep acceptors of Ga site. If this hypothesis is right same phenomena will happen in un-doped semi-insulating GaAs substrate.

Figure 28: Wafer provider dependency of photoluminescence spectra near 1.3 - 1.45 eV.

# Chapter 5

# Thermal conversion in un-doped GaAs

## 5.1 Electrical properties in thermally treated un-doped GaAs

Conductive type conversion is sometimes reported in semi-insulating GaAs substrate after the high temperature annealing. These are, for instance, the n-type conversion in Cr-doped semi-insulating HB grown GaAs [11, 35] and p-type conversion in un-doped LEC grown GaAs [36, 37]. In the former case, a semi-insulating property is brought about by compensating the Si donor which is coming from the silica boat in the HB method growth with the Cr acceptor intentionally doped. N-type conversion after annealing above 800 °C in this case is interpreted that the balance of  $N_d(Si)-N_a(Cr)$  is collapsed by the out-diffusion of Cr during the high temperature annealing. In the latter case, namely in LEC grown GaAs, semi-insulating property consists of the balance with C<sub>As</sub> acceptors and the EL2 donor derives from excess As. Therefore, p-type conversion in high temperature is said to be a result of out-diffusion of excess As.

Thus the thermal conversion is complicatedly depending on the nature of the semi-insulating. It is very important to know how the semi-insulating property is obtained and what kind of impurities contains. In this paper un-doped LEC grown GaAs is used and Mn pile up is observed in the Si-implanted samples only under H<sub>2</sub> ambient annealing. The samples are prepared for the thermal conversion experiments from the same lot of un-doped GaAs used in Chapter 3 and 4. The anneal experiments are performed in both Ar and H<sub>2</sub> ambient and in the temperature of 800 °C and 900 °C.

Table 4: Sheet carrier concentration of thermally converted samples versus atomic concentration of Mn calculated from SIMS.

| Carrier Gas | Set-up | P <sub>AsH3</sub><br>(Torr) | Temp.<br>(°C) | Ns<br>(× $10^{12} \mathrm{cm}^{-2}$ ) | Mn<br>(× 10 <sup>12</sup> cm <sup>-2</sup> ) |

|-------------|--------|-----------------------------|---------------|---------------------------------------|----------------------------------------------|

| $H_2$       | FU     | -                           | 800           | 1.6                                   | 0.54                                         |

| $H_2$       | FU     | 3                           | 900           | 1.4                                   | 2.3                                          |

| Ar          | FU     | -                           | 800           | no conversion                         | 0.04                                         |

| Ar          | FU     | 3                           | 900           | 0.15                                  | 0.13                                         |

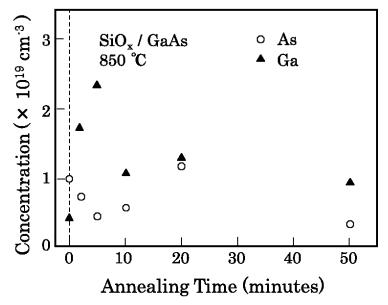

All the annealing time is 15min and 3 Torr partial pressure by  $AsH_3$  is applied in the case of 900 °C to avoid dissolution of As. The evaluated results by Van Der Paw method is summarized in Table 4. All the samples show p-type conversion excepting the samples annealed in Ar ambient at 800 °C. The extent of p-type conversion is apparently proportional to the annealing temperature and the  $P_{H2}$ . The weak conversion in Ar /AsH<sub>3</sub> ambient at 900 °C is considered to be due to H<sub>2</sub> induced by dissolution of AsH<sub>3</sub>. The results of the thermal conversion also support that annealing in H<sub>2</sub> ambient closely related to the formation of p-type carrier.

### 5.2 SIMS analysis in thermally converted samples

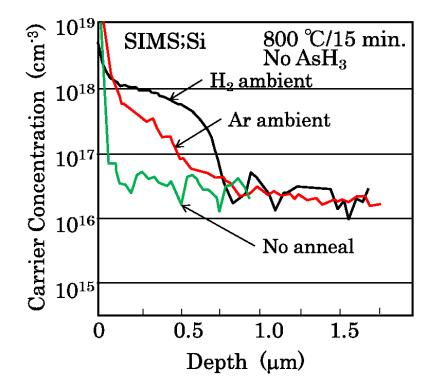

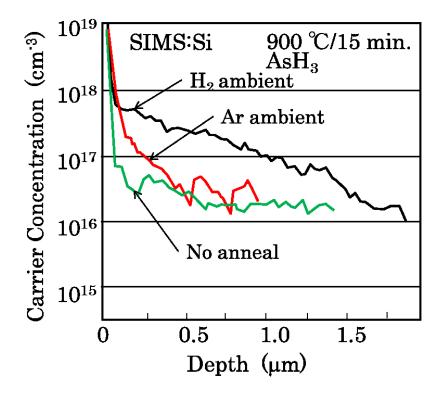

Mn distribution analysis is performed same as Chapter 4 using SIMS analysis method. The measured results are shown in Figure 29 and Figure 30 in the case of 800 °C and 900 °C annealing respectively. In both figures the dashed line is a result of no annealed samples. It is quite clear that the Mn piles up also near in the surface and that the extent of pile up is getting larger as the temperature and the  $H_2$  partial pressure increasing. In order to confirm the quantitative contribution of Mn concentration to the p-type concentration, the sheet concentration of Mn piled up is calculated by the integration of Mn in Figure 29 and 30. The results are shown in Table 4 too. The sheet carrier concentration of p-type is well accordance with Mn sheet concentration in the case of 900 °C annealing. However, in the 800 °C / $H_2$  annealing, that of p-type is 3 times larger compare to the Mn sheet concentration. It is slightly curious results and implies that there would be other factor not to be perfectly grasped.

The Si distribution is also investigated in order to clarify the inconsistency in the Table 4 by using SIMS analysis too. For the detection of the Si, Cs<sup>+</sup> ion is used as a 1st order ion source. The results are shown in Figure 31 and 32 in the case of 800 °C and 900 °C respectively. The results are marvelous because a lot of Si atoms are accumulated simultaneously near the surface both in the case of 800 °C and 900 °C annealing. Especially, the concentration of Si attains in the vicinity of  $10^{18}$  cm<sup>-3</sup> with the case of 800 °C / H<sub>2</sub> annealing as is shown in Figure 31. The Si concentration attains order of  $4 \times 10^{17}$  cm<sup>-3</sup> even in the case of 800 °C / Ar as is shown in Figure 31 too. The concentration of Si in the case of 900 °C is also high as is shown in Figure 32 although the level of accumulation is lower than the case of 800 °C. This may come from the effect of the As over pressure. Almost the detected Si must be not in the site of Ga because all the samples show p-type. The possibility of the status of Si left is the case in As site or interstitial. The Si distribution in the Figure 31 and 32 indicates very fast diffusion coefficient if the Si is not coming from outer side but through the

Figure 29: Mn depth profiles of un-doped GaAs measured by SIMS after 800 °C / 15 min annealing.

Figure 30: Mn depth profiles of un-doped GaAs measured by SIMS after 900 °C / 15 min annealing.

Figure 31: Si depth profiles of un-doped GaAs measured by SIMS after 800  $^{\rm o}{\rm C}$  / 15 min annealing.

Figure 32: Si depth profiles of un-doped GaAs measured by SIMS after 900 °C / 15 min annealing.

substrate. If almost the Si is in the interstitial site Si does not acts as both accepter and donor, furthermore, very fast diffusion constant is also well explained. At the same time the large Si accumulation in 800 °C annealing is explained by the increasing of Si<sub>As</sub> acceptor because there is no As over pressure. This assumption is well in accordance with the result of 800 °C / H<sub>2</sub> in Table 4. Furthermore, we must pay attention to the fact that the profile of Si in Figure 31 and Figure 32 is very similar to that of Mn in Figure 29 and Figure 30. These facts suggest strongly that Si and Mn diffuse same way and affecting each other. One of the possibilities is making a kind of pair of Mn and Si because  $Mn_{Ga}$  acts as - charge and Si<sub>Ga</sub> acts as + charge in the high temperature.

In order to clarify the accumulation mechanism of Mn it is useful to investigate the thermal properties of Si in GaAs. One of the important factors is to know the site position of Si in GaAs and how it is changed by the thermal treating. Regarding the site position of Si there are three possibilities, these are  $Si_{Ga}$ ,  $Si_{As}$  and interstitial. The studies using RBS/PIXE method is very effective to determine the site position of the dopant in Zincblende structure. In the next chapter the results of the site position evaluated by RBS/PIXE is described.

## Chapter 6

# Crystallographic studies by RBS/PIXE

## 6.1 Basis in RBS and PIXE analysis

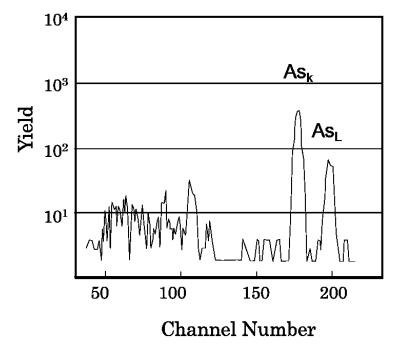

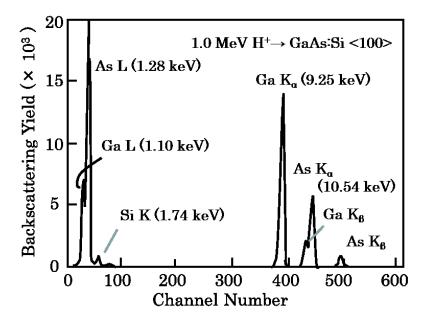

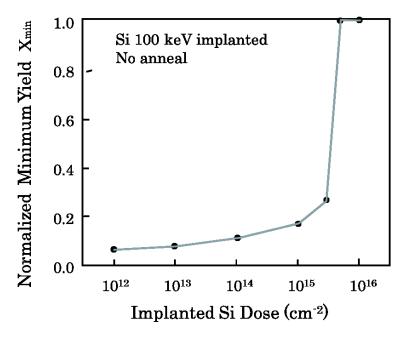

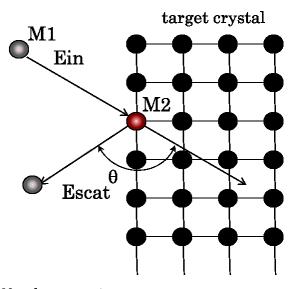

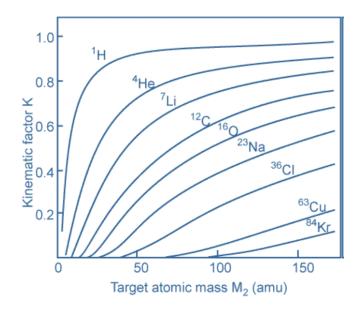

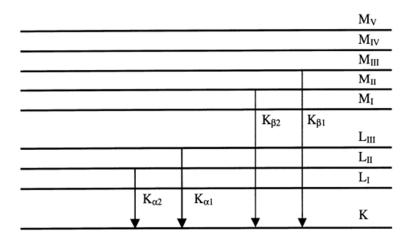

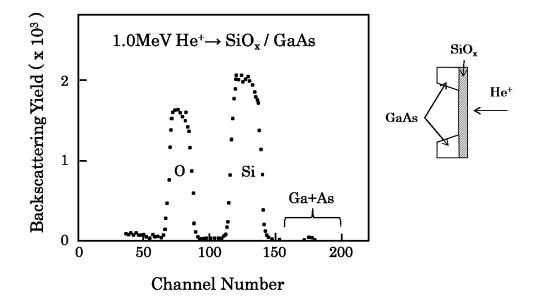

In order to investigate the status of the implanted Si RBS/PIXE analysis is employed. RBS (Rutherford backscattering spectroscopy) is well known as an analysis method which can evaluate the crystallography. It can estimate quantitative atomic density by analyzing the energy distribution of the back scattered probe atoms. Normally, He<sup>+</sup> or H<sup>+</sup> are used as probing ions and this probing ion have an energy information of target atoms because the backscattering can be considered as a results of perfect elastic collision. The limit of detection is about an order of  $10^{18}$  cm<sup>-3</sup> and it is relatively lower sensitivity because the probability of the complete elastic collision is extremely low. On the other hand, PIXE (particle-induced x-ray emission) can analyze the species of target atoms by analyzing the energy of characteristic x-ray emission. Furthermore, we can analyze the crystallography or identify the position of dopant by utilizing the asymmetry of the crystal and the channeling effect. All the experiments in this Chapter are performed under the collaboration with research laboratory have a Van de Graaff accelerator in Hokkaido University. The samples prepared here are (100) oriented un-doped LEC grown GaAs too. The Si ion implantation performed with the energy

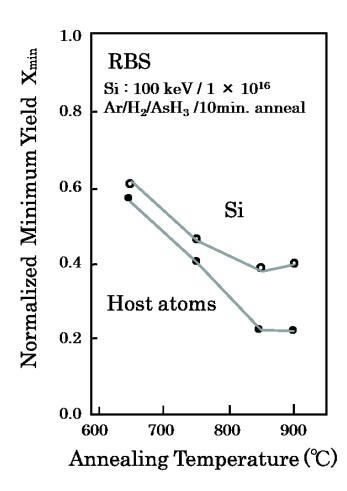

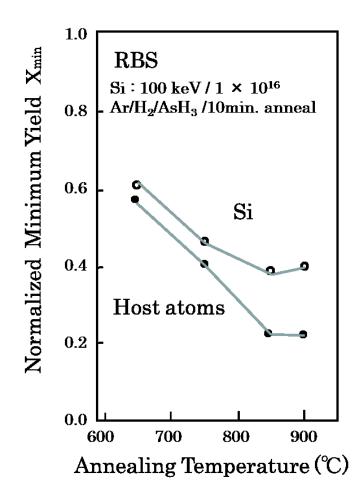

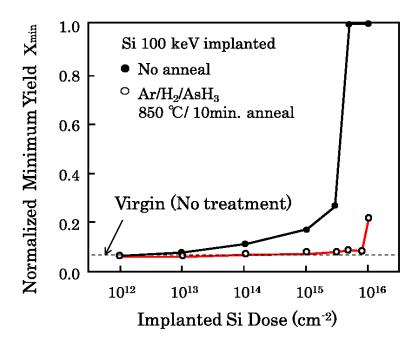

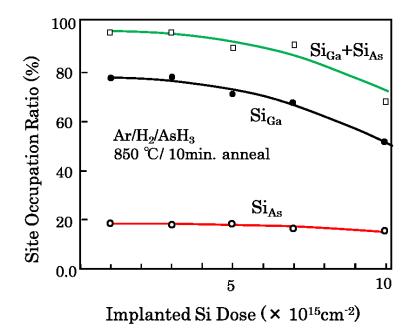

Figure 33: Typical RBS spectrum versus annealing temperature.

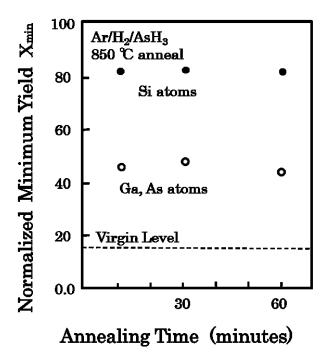

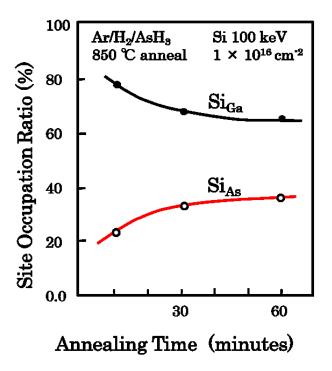

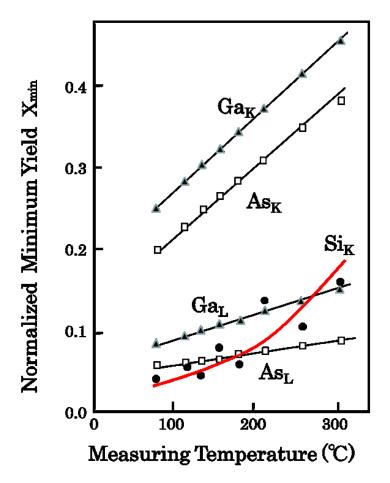

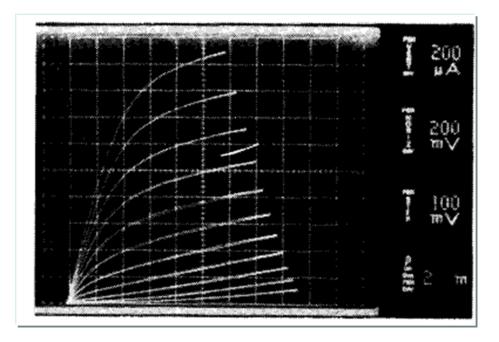

of 100 keV and the dose is varied with the range of  $1 \times 10^{15}$  to  $1 \times 10^{16}$ . Annealing at 750 °C, 850 °C, 900 °C and 10 minutes is performed in H<sub>2</sub>/Ar/AsH<sub>3</sub> ambient with FF configuration.